Тема лекции 14. Сигнальные процессоры. Основы цифровой обработки сигналов. Аналогово-цифровые и цифро-аналоговые преобразователи. Сигнальные процессоры DSP (digital signal prossor). Классификация, назначения.

Сигнальные процессоры предназначены в основном для цифровой обработки сигналов (ЦОС).

ЦОС – это арифметическая обработка в реальном масштабе времени последовательности значений амплитуды сигнала через равные временные промежутки. Примерами цифровой обработки являются:

- фильтрация сигнала;

- свертка двух сигналов;

- вычисление значений корреляционной функции двух сигналов;

- усиление, ограничение или трансформация сигнала;

- прямое/обратное преобразование Фурье сигнала.

Основным входным устройствос сигнальных процессоров является аналого-цифровой преобразователь,а выходным устройством - цифро-аналоговый преобразователь.

Аналогово-цифровое преобразование.

Непрерывный аналоговый сигнал – это сложное по форме колебание, некая зависимость амплитуды сигнала от времени. Преобразование аналогового сигнала в цифровой вид называется аналогово-цифровым преобразованием или оцифровкой. Процесс такого преобразования заключается в осуществлении замеров величины амплитуды аналогового сигнала с некоторым временным шагом (дискретизация) с последующей записью измеренных значений амплитуды в численном виде (квантование).

Дискретизация по времени и квантование по уровню лежат в основе преобразования сигнала из аналоговой формы в цифровую.

Временная информация кодируется в цифровой системе путем периодического измерения мгновенных значений аналогового сигнала. Дискретное значение аналогового сигнала называют отсчетом. Амплитудная информация кодируется в результате представления значения каждого отсчета при помощи числа. Этот процесс называется квантованием. Таким образом, дискретизация сохраняет временную информацию, квантование — амплитудную.

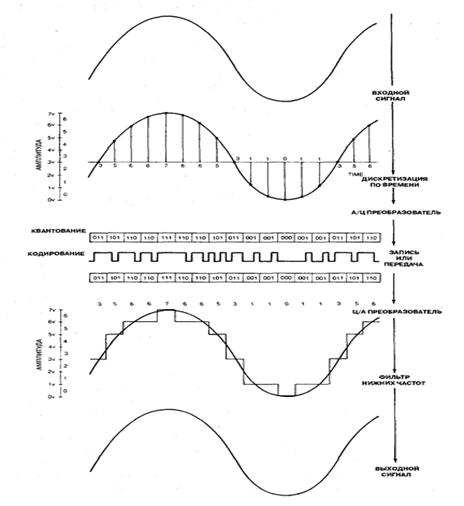

В результате выполнения дискретизации по времени и квантования по уровню возникает последовательность двоичных чисел, называемых словами, которые представляют форму аналогового сигнала. Если преобразовать эти двоичные слова обратно в напряжение с сохранением исходных параметров первоначальной дискретизации по времени, то приблизительно будет воссоздана форма аналогового звукового сигнала. Таким образом дискретизация по времени и квантование по уровню преобразуют непрерывную аналоговую функцию (непрерывно изменяющееся напряжение аналогового сигнала) в последовательность дискретных двоичных чисел. На рис. 15-1 показано, как непрерывный аналоговый сигнал преобразуется в двоичные числа и обратно в непрерывный аналоговый сигнал.

Рис. 15.1. Схема аналогово-цифрового и цифро-аналогового преобразования

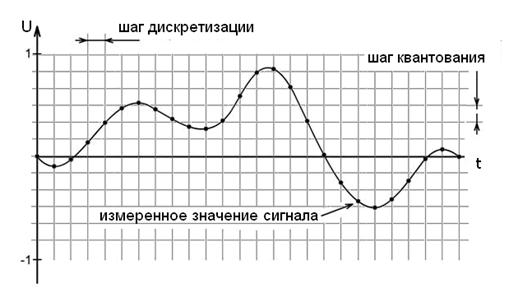

Процесс дискретизации по времени – это процесс получения мгновенных значений преобразуемого аналогового сигнала с определенным временным шагом, называемым шагом дискретизации (см рис. 15.2).

Рис. 15.2. Дискретизация и квантование аналогового сигнала

Количество осуществляемых в одну секунду замеров величины сигнала называют частотой дискретизации или частотой выборки. Очевидно, что чем меньше шаг дискретизации, тем выше частота дискретизации (то есть, тем чаще регистрируются значения амплитуды), и, значит, тем более точное представление о сигнале мы получаем. Это рассуждение подтверждается доказанной теоремой Котельникова. Согласно этой теореме, аналоговый сигнал с ограниченным спектром может быть точно описан дискретной последовательностью значений его амплитуды, если эти значения следуют с частотой, как минимум вдвое превышающей наивысшую частоту спектра. Для завершения процесса оцифровки теперь осталось лишь записать измеренные мгновенные значения амплитуды сигнала в численной форме. Полученная последовательность чисел (по одному результату замера амплитуды сигнала на каждый шаг) и образует цифровую форму исходного аналогового сигнала – так называемый импульсный сигнал.

Аналого–цифровым преобразователем (АЦП) называют устройство, преобразующее входную аналоговую величину в соответствующий ей цифровой эквивалент – код, являющийся выходным сигналом преобразователя. АЦП обеспечивает как дискретизацию непрерывного сигнала по времени, так и его квантование по уровню.

Исходя из этого целесообразно разделить методы построения АЦП на последовательные, параллельные и последовательно–параллельные.

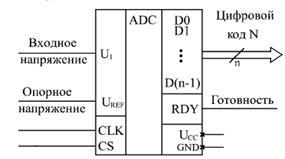

В общем случае микросхема АЦП имеет один аналоговый вход и несколько цифровых выходов (рис. 15.3). Часто микросхема АЦП имеет также вход для подачи тактового сигнала CLK, сигнал разрешения работы CS и сигнал, говорящий о готовности выходного цифрового кода RDY.

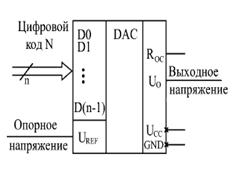

Рис. 15.3. Микросхема АЦП Рис. 15.4. Микросхема ЦАП

Микросхема ЦАП можно представить в виде блока (рис. 15.4), имеющего несколько цифровых входов и один аналоговый выход. В целом микросхемы АЦП сложнее, чем микросхемы ЦАП.

В состав сигнальных процессоров входять АЦП и ЦАП различного класса и быстродействия. Полученный после преобразования цифровой сигнал может обрабатываться различными методами. Например, процесс операции умножения двух чисел с сохранением результата в традиционных микропроцессорах является сложным. Ускорение этого процесса в процессоре общего назначения невозможна из-за наличия единственной шины адреса и единственной шины данных, а также единственного банка данных.

При цифровой обработке сигналов все эти затраты недопустимы. С целью преодоления этого недостатка процессоров общего назначения и были разработаны процессоры цифровых сигналов (DSP - Digital Signal Processor).

Ее особенность состоит прежде всего в том, что в отличии от привычных нам двух шин: шины адреса и шины данных, а также одного банка памяти, DSP имеет как минимум 6-7 различных шин и 2-3 банка памяти. Эта особенность имеет своей целью максимально ускорить выполнение операции умножения с сохранением результата, которая, несомненно, является наиболее употребляемой и ресурсоемкой при цифровой обработке сигналов. Архитектура DSP позволяет за один машинный цикл произвести:

1. выборку команды посредством шины адреса программ и шины данных программ;

2. выборку двух операндов для операции умножения посредством двух шин адреса данных;

3. занесение операндов в аккумуляторы посредством двух шин данных;

4. операцию умножения;

5. сохранить результат в аккумуляторе.

Таким образом, трехшинная Гарвардская архитектура позволяет выполнить практически любую операцию за один машинный цикл.

Однако, как уже упоминалось, процессоры цифровой обработки сигнала имеют отличием не только высокую производительность, измеряемую в быстроте выполнения операций умножения/аккумуляции (MIPS - миллионы команд в секунду), но и такие характеристики, как последовательность выполнения программ, арифметических операций и адресации памяти, позволяющие сократить до минимума непроизводительные затраты времени.

Алгоритмы DSP включают очень много повторяющихся операций, которые могут быть реализованы в виде циклов. Возможность организации последовательности выполнения программы кодов в цикле без потери производительности отличают DSP от других процессоров. Аналогично, потеря времени при выполнении операции ветвления по условию также недопустима при цифровой обработке сигналов.

Фирмой Motorola в настоящее время выпускается три семейства Цифровых Процессоров Сигналов. Это серии DSP56100, DSP56000 и DSP96000. Все микросхемы приведенных серий основываются на архитектуре DSP56000 и различаются разрядностью (16, 24, 32 бит соответственно) и некоторыми встроенными устройствами. Таким образом достигается совместимость микросхем всех трех семейств снизу вверх. Все DSP фирмы Motorola построены по идентичной трехшинной Гарвардской архитектуре.

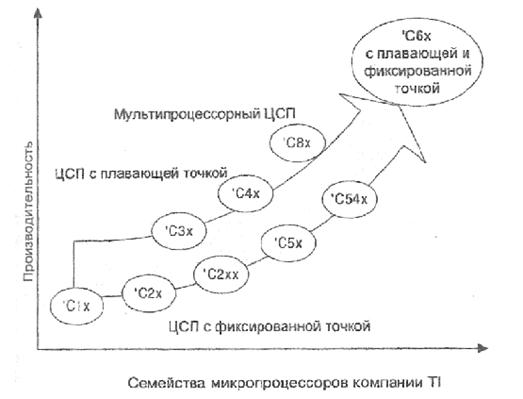

DSP фирмы Texas Instruments представлены следующими микропроцессорами: TMS 32010, TMS 320C20, TMS 320C25, TMS 320C30, TMS 320C40, TMS 320C50.

Рис. 15.5. Семейство микропроцессоров компании TI

В основу микропроцессора TMS320C10положена модифицированная гарвардская архитектура, отличием которой от традиционной гарвардской архитектуры является возможность обмена данными между памятью программ и памятью данных, что повышает гибкость устройства. TMS320C10 является 16-разрядным процессором. Его адресное пространство составляет 4 Кслов памяти программ и 144 слова памяти данных. Все слова имеют разрядность 16. Длительность командного такта процессора составляет 160-200 нс.

Арифметические функции в процессоре реaлизованы аппаратно. Он имеет аппаратные умножитель (MULT), устройство сдвига (SHIFTER), аппаратную поддержку автоинкремента/декремента адресных регистров данных(ARO, ARl).С внешними устройствами процессор взаимодействует через 8 портов ввода/вывода. Каждый порт имеет разрядность 16. Предусмотрена возможностьобработки внешних прерываний.

Микропроцессор TMS320C80, выпушенный в конце 1994 года, имеет второе название - MVP (Мultiшеdiа Video Pгocessor - мультимедийный видеопроцессор), что обусловлено его высокой эффективностью на задачах обработки изображений, в системах виртуальной реальности, компрессии и декомпрессии видео- и аудиоданных, обработки связной информации.

TMS320C80 представляет собой новый подход к повышению производительности и,функциональности цифровых сигнальных процессоров: в одной микросхеме объединено четыре усовершенствованных цифровых процессора обработки сигналов (ADSP - Advanced Digital Signal Pгocessor), каждый из которых выполняет за такт несколько RISС-операций, и пятый процессор, называемый главным процессором (Master Processor), - 32-разрядный процессор с высокопроизводи ельным устройством обработки чисел вформате с плавающей точкой.

Микропроцессоры семейства ADSP21xx успешно конкурируют с аналогичной продукцией компаний Motorola и Texas Iпstгuшепts благодаря высокой производительности и низкой цене, а также наличию развитых аппаратных и программных средств разработки прикладных систем. Микропроцессоры ADSP21xx имеют модифицированную гарвардскую архитектуру, в рамках которой предусматривается возможность доступа в память команд при ее физическом разделении с памятью данных.

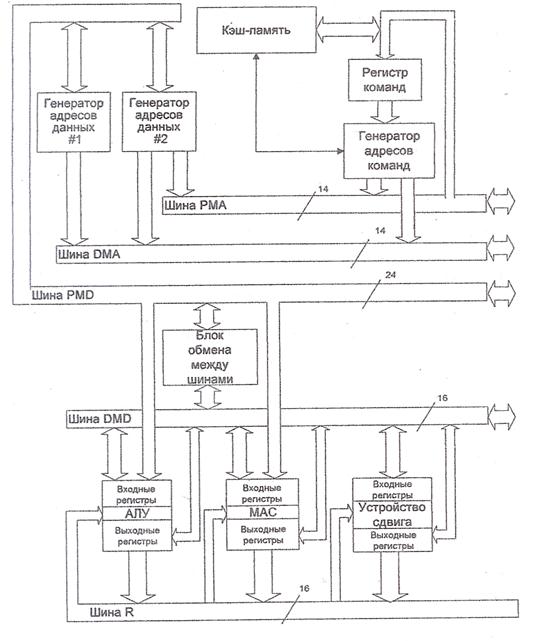

Каждый микропроцессор семейства содержит три независимых функциональных блока: АЛУ, умножитель с накоплением (МАС) и устройство барабанного сдвига. Каждый блок непосредственно оперирует с 16-разрядными данными и обеспечивает аппаратную поддержку вычислений с различной точностью.

Микропроцессор содержит генератор адресов команд и два генератора адресов данных, обеспечивающие адресацию к данным и командам, расположенным как во внутренней, так и во внешней памяти. Параллельное функционирование генераторов сокращает длительность выполнения команды, позволяя за один такт выбирать из памяти команду и два операнда (рисю 15.6.).

Рис. 15.6. Структура микропроцессора ADSP219xx

Последовательные порты обеспечивают интерфейс с большинством стандартных последовательных устройств, а также с аппаратными средствами сжатия/восстановления данных, использующими А- и н-законы компандирования.

Порт интерфейса с хост-процессором позволяет без дополнительных интерфейсных схем взаимодействовать с хост-процессором системы, в качествекоторого может использоваться как процессор данного семейства, так идругой микропроцессор.

Микропроцессор ADSP-21msp5x отличается наличием аналогового интерфейса, позволяющего вводить и выводить обрабатываемый сигнал в 'аналоговой форме. В состав интерфейсных блоков входят ЛЦП, ЦАП, цифровойи аналоговый фильтры, параллельный интерфейс.

Общее для семейства ADSP-21xx микропроцессорное ядро изображено на рис. 15.6. Арифметико-логическое устройство микропроцессора выполняет стандартный набор арифметических и логических операций, включая деление. Устройство МАС выполняет операции умножения со сложением(вычитанием) за один такт. Устройство сдвига осуществляет арифметические и логические сдвиги операндов, нормализацию и возведение в степень. Функциональные устройства микропроцессора могут обмениваться результатами выполнения операций по шине внутренних результатов.

Внутренние функциональные блоки связаны между собой с помощью пяти шин: шина адресов памяти данных (ОМА), шина адресов памяти команд (РМА), шина данных памяти данных (ОМО), шина данных памяти команд (РМО) шина внутренних результатов (R). Первые четыре шины имеют мультиплексированной внешний интерфейс в виде шины адреса и шины данных (см. рис. 15.6).

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Назначение аналогово-цифрового преобразователя?

2. Что такое дискретизация?

3. Что такое квантование?

4. Что такое цифровая обработка сигналов?

5. Из скольких серий состоит процессоры цифровой обработки DSP?

6. Состав DSP фирмы TI?

7. Основные функций и состав АDSP219 х?

Коммуникационные процессоры – это микрочипы, представляющие собой нечто среднее между жесткими специализированными интегральными микросхемами и гибкими процессорами общего назначения. Коммуникационные процессоры программируются, как и привычные для нас ПК-процессоры, но построены с учетом сетевых задач, оптимизированы для сетевой работы и на их основе производители – как процессоров, так и оборудования – пишут программное обеспечение для специфических приложений. Коммуникационный процессор имеет собственную память и оснащен высокоскоростными внешними каналами для соединения с другими процессорными узлами. Скоростной коммуникационный процессор с RISC-ядром позволяет управлять обменом данными по нескольким независимым каналам, поддерживать практически все распространенные протоколы обмена, гибко и эффективно распределять и обрабатывать последовательные потоки данных с временным разделением каналов.

Коммуникационный контроллер MC68360 (QUICC)

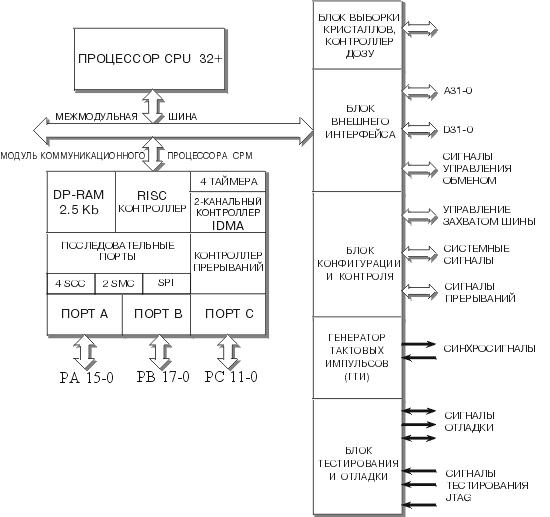

Наиболее широкими возможностями обладает контроллер MC68360, использующий 32-разрядный процессор CPU32+ и модуль коммуникационного процессора CPM, который является расширенным вариантом СP. Этот контроллер, который получил название QUICC (Quad Integrated Communications Controller), рассматривается подробно.

Контроллер MC68360 и его модификации MC68EN360, MC68MH360 имеют модульную структуру (рис. 15.1), в которую входят центральный процессор CPU32+, модуль коммуникационного процессора CPM и модуль системной интеграции SIM60, соединенные общей внутренней шиной.

Рис. 15.1. Общая структура коммуникационного процессора MC68360.

Центральный процессор CPU32+

Процессор CPU32+ имеет архитектуру, принятую в микропроцессорах семейства 68000, что позволяет использовать большой объем программного обеспечения, созданный для этого семейства. Процессор обеспечивает работу с 32-разрядными шинами адресов и данных, аналогично MС68020 и более поздним моделям семейства 68000.

Архитектура процессора ориентирована на раздельное выполнение двух классов задач: управление работой системы с помощью супервизора(операционной системы) или решение прикладных задач пользователя.. В режиме супервизора разрешается выполнение любых команд, реализуемых процессором, и доступ ко всем его регистрам. В режиме пользователя запрещается выполнение ряда команд и доступ к некоторым регистрам, чтобы не допустить такие изменения состояния системы, которые могут помешать выполнению других пользовательских программ или нарушить режим работы процессора, установленный супервизором.

Процессор CPU32+ выполняет набор из 158 команд, которые реализуют пересылку данных, арифметические и логические операции, сдвиги, операции сравнения и тестирования, битовые операции, операции управления и условной установки байтов. Часть команд выполняется только в режиме супервизора. Это привилегированные команды, попытка выполнения которых в режиме пользователя вызывает прерывание программы.

В набор команд включены команды интерполяции, которые вычисляют значения линейной функции в 255 промежуточных точках отрезка, для которого задаются конечные значения. Таким образом исключается необходимость хранения в памяти промежуточных значений линейных функций. Процесор CPU32+ не имеет специальных команд ввода-вывода данных. Для обращения к внешним устройствам их адрес формируется и выдается на адресную шину, как при выборке ячеек памяти.

Процессор CPU32+ реализует обслуживание программных исключений, возникающих при выполнении некоторых команд, и аппаратных исключений, которые вызываются внешними запросами или внутренними сигналами, формируемыми при возникновении ряда ситуаций.

Во всех этих ситуациях процессор заносит в стек кадр определенного формата, содержимое которого обеспечивает возвращение к прерванной программе. Стековый кадр имеет размер от 4 до 12 байт, и содержит текущие значения регистров PC и SR, код формата Fe и адрес вектора прерывания Av, а также дополнительную информацию, которая помогает подпрограмме обслуживания определить причину исключения.

После загрузки стека в PC заносится из памяти вектор исключения Ve - начальный адрес подпрограммы обслуживания. Эти вектора хранятся в таблице, базовый адрес которой содержится в регистре VBR. Каждое исключение имеет свой номер Ne, который принимает значения от 0 до 255. Значение Ne, сдвинутое на два разряда влево, дает относительный адрес вектора в таблице исключений. Таблица может иметь объем до 1024 байт и содержать адреса входов для 254 подпрограмм обслуживания.

Специфические особенности функционирования и применения MC68360 и его модификаций MC68EN360, MC68MH360 связаны с наличием в их составе коммуникационного процессора CPM, который содержит большой набор интерфейсных блоков, обеспечивающих возможности подключения контроллера к линиям связи с различными протоколами обмена.

Модуль CPM подключается к внутренней шине и работает под управлением собственного RISC-контроллера с минимальным вмешательством процессора CPU32+. Основное назначение CPM - обеспечить разнообразные каналы параллельной и последовательной передачи данных между микропроцессорной системой, управление которой осуществляет CPU32+ через интерфейсный модуль SIM60, и внешними устройствами, подключенными с помощью линий связи с различными протоколами обмена. Коммуникационный контроллер может работать в режиме ведомого (slave). В этом режиме его CPU отключается, и модуль CPM функционирует под управлением внешнего процессора. Таким образом можно реализовать систему из нескольких CPM (контроллеров в режиме ведомого), работающих под управлением одного ведущего процессора.

КМК МС68302 содержит встроенный коммуникационный процессор, самостоятельно выполняющий программы по обработке практически любого протокола связи (см. рис. 15.2).

Рис.15.2. Структура коммуникационного контроллера MC68302

В ПЗУ микрокода изначально содержатся программы, поддерживающие наиболее распространенные протоколы: HDLC, BISYNC, UART, Transparent и другие. Кроме того, программы могут выполняться из двухпортового ОЗУ, что позволяет реализовать практически любой нестандартный протокол и делает данный КМК чрезвычайно универсальным. Три независимых коммуникационных контроллера (SCC) имеют индивидуальные каналы прямого доступа к памяти как на прием, так и на передачу. Взаимодействие со встроенным управляющим процессором 68000 осуществляется через двухпортовое ОЗУ емкостью 1152 байт, половина которого используется для указателей входных/выходных буферов, а вторая половина может использоваться для хранения данных или загрузки микрокода. Коммуникационный процессор обеспечивает одновременную работу всех трех каналов, причем каждый из них может обрабатывать любой из протоколов. Помимо поддержки логических протоколов, МС68302 имеет блок сопряжения с физическими интерфейсами: немультиплексируемый интерфейс с поддержкой модемных сигналов (NMSI) и интерфейсы с временным мультиплексированием, например, ИКМ или ISDN BRI (IDL и GCI). Производительность МС68302 позволяет обрабатывать потоки информации до 2 Мбит/с. Помимо основных последовательных каналов (SCC), МС68302 содержит два контроллера управления обменом SМС, поддерживающие работу с IDL или GCI, а также синхронный последовательный интерфейс SCP.

Управляющий процессор 68000 является базовой моделью широко распространенного семейства 680х0, что предоставляет в распоряжение пользователя огромный выбор апробированного программного обеспечения: от кросс-ассемблеров до операционных систем реального времени, а также готовых аппаратных и программных решений.

Блок системной интеграции позволяет подключать внешние устройства и память с минимальными аппаратными затратами и содержит независимый канал ПДП общего назначения, контроллер прерываний, таймеры, тактовый генератор, программируемые выборки внешних устройств, контроллер регенерации динамической памяти.

МС68360 выпускается в нескольких модификациях, среди которых в первую очередь можно выделить МС68МН360. Этот контроллер поддерживает до 32 каналов HDLC на одном SCC, что позволяет легко обрабатывать потоки данных с временным разделением каналов, например, ИКМ-30 или ISDN PRI. Типичными применениями МС68MH360 являются: оборудование ИКМ, цифровые АТС различного уровня, сетевое оборудование, станции сотовой связи. МС68EN360 поддерживает Ethernet на любом из каналов SCC, обеспечивая функции контроля доступа к среде (MAC), полную обработку коллизий, обнаружение длинных фреймов и другие функции при скорости обмена до 10 Мбит/с.

Сетевые процессоры

Процессоры серии IXP12хх являются представителями семейства сетевых процессоров, производимых компанией Intel в рамках IXA.

Архитектура Internet Exchange включает в себя следующие компоненты:

- сетевые процессоры серии IXP;

- коммутационные контроллеры приложений серии IXE для сетей ATM, Gigabit и 10/100Mb Ethernet. Эти высокопроизводительные устройства предоставляют системным разработчикам возможность сократить сроки поставки своей продукции на рынок и обеспечить ее полную совместимость с новейшими общепринятыми стандартами;

- форматирующие устройства серии IXF для форматирования ячеек ATM, фреймов T1/E1 и Sonet/SDH, пакетов данных Gigabit и 10/100Mb Ethernet;

- компоненты физического уровня серии LXT для сопряжения сетевых устройств, работающих в стандартах T1/E1, HDSL, HDSL2, Sonet/SDH PHYs, 10/100Mb Ethernet, Gigabit (в том числе основанные на медной технологии). Процессоры IXP

По мере смешения голосовых сетей и сетей передачи данных, пересечение открытых и частных сетей все острее требует от производителей оборудования создания основанных на открытых стандартах устройств, способных поддерживать несколько услуг одновременно. По мере того, как повышаются требования поставщиков услуг к интеллектуальности и гибкости сетей, все отчетливее ощущается важность наличия в центре сервисной инфраструктуры перепрограммируемых сетевых процессоров.

Каждый тип процессоров представлен определенным семейством, включающим несколько его модификаций. Семейство процессоров IXP представлено более чем пятью моделями, основное отличие которых заключается в производительности, а следовательно, и пригодности для создания различного телекоммуникационного оборудования. Процессоры 12хх относятся к простейшей линейке сетевых процессоров IXP.

Сетевой процессор IXP1200

Ключевым элементом архитектуры IX является сетевой процессор IXP1200, совместимый со всем спектром коммутирующих и форматирующих устройств, а также компонентов физического уровня. Шина IX сетевого процессора IXP1200 позволяет поручить ему выполнение сложных сетевых функций (например, контроль за шифрованием и обеспечением качества обслуживания), освободив от них коммутирующие устройства IXE в целях соблюдения приоритетности и обеспечения управления.

Сетевому процессору IXP1200 отводятся функции обработки, преобразования и маршрутизации пакетов данных, передаваемых по сетям всех типов. Сетевой процессор IXP1200 обладает мощностью, достаточной для выполнения вычислений в процессе передачи данных, а также определенных задач управления сетевой системой.

Сетевой процессор IXP1200 объединил в себе два вычислительных компонента, играющих важную роль в большинстве сетевых систем: встроенный микропроцессор и контроллеры передачи данных со скоростью, сравнимой с кабельной трансляцией.

Встроенный микропроцессор StrongARM, совместимый с 32-разрядной архитектурой ARM®, служит для выполнения задач управления сетью, 6 программируемых микроконтроллеров ведут многопоточную обработку данных, перемещаемых по сети со скоростью трансляции по кабелю. Одновременно могут выполняться 7 различных сетевых задач, а 18 других ставятся в очередь для выполнения в течение одного цикла. Такая контекстно-зависимая подкачка в режиме нулевого ожидания обеспечивается специализированными инструкциями микроконтроллеров.

Каждый процессор IXP1200 способен направлять 3 млн пак/с, а с учетом объединения нескольких процессоров, производительность системы составит 1,5 Тбит/с.

IXP1200 можно применять в разработке маршрутизаторов, переключателей и концентраторов, поддерживающих такие протоколы передачи данных, как Gigabit Ethernet, Sonet и ATM.

Архитектура IXP1200

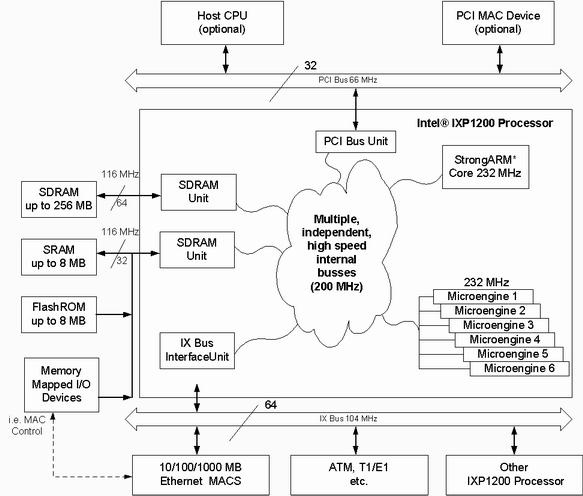

Кристалл процессора IXP1200 содержит процессорное ядро StrongARM и 6 независимых 32-битных RISC микропроцессоров, устройства SRAM, SDRAM, PCI и IX контроллеры шины (рис. 15.3).

Рис.15. 3. Структурная схема процессора IXP1200

Операционные частоты 166–232 МГц. Производительность процессора составляет 3 млн пак/с, что дает 1,5 Гбит/с. Производительность может быть увеличена, если организовать подключение нескольких процессоров параллельно. Таким образом, объединив 8 процессоров можно достичь производительности 24 Mpps.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Назначение коммуникационных процессоров?

2. Назначение сетевых процессоров?

3. Структура и состав коммуникационного процессора MC68360?

4. Структура и состав сетевого процессора IXP1200?

5. дискретизация?

6. Особенности коммуникационных процессоров?

7. Особенности сетевых процессоров?

Экзаменационные вопросов по курсу:

1. Способы представления Булевых функций.

2. Булевые функций одной переменной.

3. Булевые функций от двух переменных.

4. Минимизация булевых функций

5. Основные формы представления чисел.

6. Представление чисел с фиксированной запятой.

7. Представление чисел с плавающей запятой.

8. Кодирование десятичных чисел.

9. Перевод чисел из одной системы счисление в другую.

10. Операция сложения двоичных чисел.

11. Операция сложения двоичных чисел в системе 2421.

12. Операция сложения двоичных чисел в системе 8421+3.

13. Операция сложения двоичных чисел в системе 8421+6.

14. Операция вычитания двоичных чисел.

15. Операция вычитания двоичных чисел в системе 2421.

16. Операция вычитания двоичных чисел в системе 8421+3.

17. Операция вычитания двоичных чисел в системе 8421+6.

18. Операция умножения двоичных чисел.

19. Операция деления двоичных чисел.

20. Особенности выполнения операции умножения десятичных чисел.

21. Особенности выполнения операции деления десятичных чисел.

22. Комбинационные схемы.

23. Анализ и синтез комбинационных схем.

24. Последовательные схемы – элементарные автоматы.

25. Автомат Миля.

26. Автомат Мура.

27. Схемы И,ИЛИ и НЕ, таблицы истинности.

28. Дешифраторы.

29. Шифраторы.

30. Мультиплексоры.

31. Демультиплексоры.

32. Компаратор.

33. Запоминающие элементы.

34. RS- триггер.

35. JK- триггер.

36. D- триггер.

37. DV- триггер.

38. T- триггер.

39. TV- триггер.

40. Однотактные триггеры.

41. Двухтактные триггеры.

42. Регистры. Классификация.

43. Последовательный регистр

44. Параллельный регистр.

45. Регистр сдвига.

46. Универсальный регистр.

47. Счетчики. Классификация.

48. Последовательные счетчики.

49. Прямые и обратные счетчики.

50. Полусумматор.

51. Полный одноразрядный сумматор.

52. Многоразрядный последовательный сумматор,

53. Многразрядный накпливающий сумматор.

54. Арифметическое-логическое устройство.

55. Запоминающие укстройства (ЗУ). Классификация.

56. Оперативные ЗУ.

57. Постоянные ЗУ.

58. Сверхоперативное ЗУ.

59. Статическое ОЗУ.

60. Динамическое ОЗУ.

61. Микропроцессор (МП). Определение и классификация.

62. Командный цикл МП.

63. Машинный цикл МП.

64. Машинный такт.

65. Основной состав и принцип работы МП.

66. Запись информации.

67. Считывание информации.

68. Процесс прерывания.

69. Прямой доступ к памяти (ПДП).

70. МП Intel 8080.

71. МП Intel 8086.

72. МП Intel 8085.

73. МП Intel 80286.

74. МП Intel 80386.

75. МП Intel 80486.

76. МП Pentium.

77. Микропроцессорная система (МПС). Определение и классификация.

78. Основной состав и принцип работы МПС.

79. Основное ядро МПС.

80. Шинные формирователи.

81. Контроллер ввода с клавиатуры и вывода на индикаторы.

82. Контроллер последовательного ввода/вывода.

83. Контроллер прямого доступа к памяти.

84. Контроллер параллельного ввода/вывода информации.

85. Сопроцессоры.

86. Микроконтроллер. Определение и классификация.

87. Микроконтроллеры с CISC архитектурой.

88. Микроконтроллеры с RISC архитектурой.

89. Сигнальный процессор. Определение и классификация.

90. Интерфейсы микро-ЭВМ.

91. Интерфейс PCI.

92. Однокристальный микро-ЭВМ МК48.

93. Однокристальный микро-ЭВМ МК51.

94. Пример использование МК 51.

95. Сигнальные процессоры фирмы Motorolla

96. Сигнальные процессоры фирмы Texas Instruments

97. Основные функций МП.

98. Арбитраж в интерфейсах МПС.

99. Коммуникационные процессоры.

100. Сетевые процессоры.

2014-02-24

2014-02-24 2740

2740