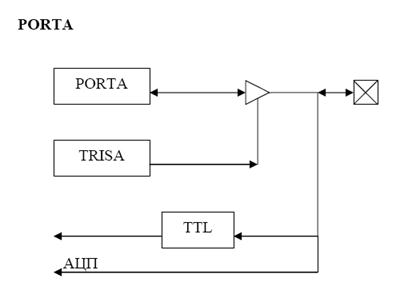

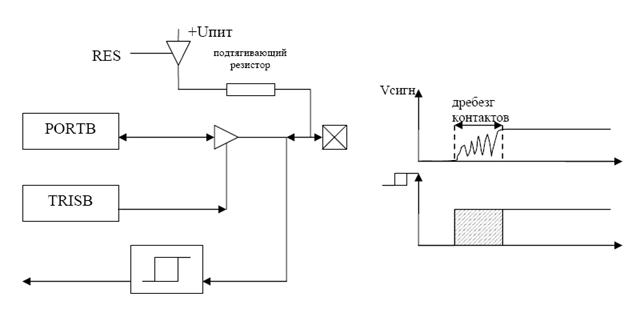

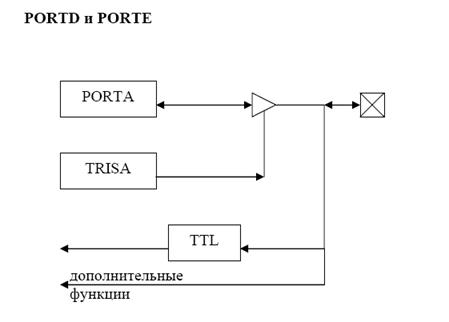

Структурные схемы портов

ТТL буфер для входящих сигналов.

РОRТА - цифровое значение входного/выходного сигнала.

ТRISА - разрешает или запрещает биты на вывод из порта

Триггер Шмита - модуль, устраняющий дребезг контактов.

Программный триггер Шмита: обеспечивает задержку на входе при обработке клавиатуры. При получении первого импульса на время t отключает прием сигнала.

ПОСЛЕДОВАТЕЛЬНЫЙ СИНХРОННЫЙ ПОРТ (МSSР)

МSSР - ведущий синхронный последовательный порт - для связи с внешними периферийными устройствами и микросхемами (ЕЕРRОМ, АЦП драйверы ЖКИ и т.д.)

МSSР имеет 2 режима:

• Последовательный периферийный интерфейс (SРI)

• I2С.

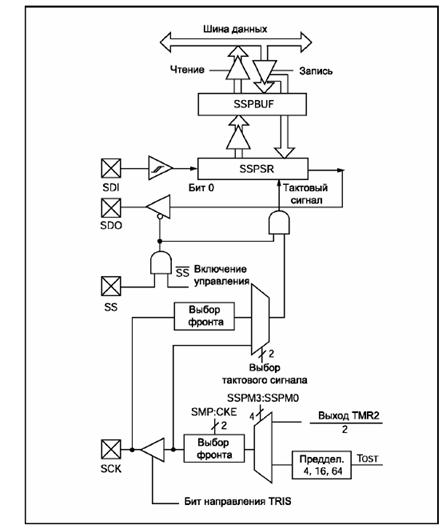

Выводы МSSР в режиме SРI:

• SDI - вход данных SРI

• SDO - выход данных SРI

• SCK - тактовый сигнал.

• -SS - выбор ведомого.

Основные режимы SPI: ведущий (SСК - выход), ведомый (SСК - вход).

Дополнительные режимы SРI: 4 режима тактирования отличающиеся полярностью и фронтом SСК; управление фазой выборки бита данных: частотой приема/передачи в режиме Маster, режим выбора ведомого в режиме Slave.

Структурная схема модуля в режиме SРI

Регистры SFR, связанные с работой SРI: управления SSРСОN, статуса SSРSТАТ и данных SSРВUF.

Регистр SSРСОN:

| WCOL | SSPOV | SSPEN | CKP | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| Бит 7 | Бит 0 |

WCOL: Флаг - Режим "ведущий" 1/0 - конфликт - попытка записи SSРВUF во время передачи/нет конфликта; "ведомый" 1/0 - конфликт - запись в SSРВUF во время передачи байта/нет конфликта;

SSPOV: 1/0 - есть/нет переполнение SSРВUF (при передаче значения не имеет);

SSPEN: 1/0 - включение/выключен не последовательного порта;

CKP: 1/0 - полярность тактирующих импульсов, ожидание высокий/низкий уровень;

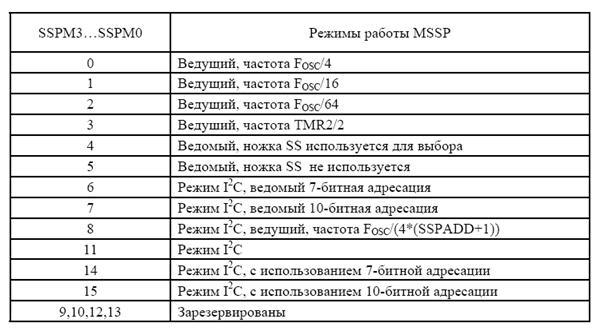

SSPM3… SSPM0: режим работы последовательного порта (ведущий/ведомый, SPI/I2C) и скорость передачи данных.

Регистр SSРSТАТ:

| SMP | CKE | D/-A | P | S | R/W | UA | BF |

| Бит 7 | Бит 0 |

SMP: 1/0 - входные данные защелкиваются в конце/середине выходных

СКЕ: Для режима SРI: при СКР=0: 1/0 - данные передаются по фронту/падению тактового импульса; при СКР=1: 1/0 - данные передаются по падению/фронту тактового импульса. Для режима I2C: 1/0 - уровни на шине соответствуют спецификации Smbus/ I2C

D/-A: последний принятый или переданный байт - данные/адрес (I2С)

Р: последний принятый бит - SТОР (I2C)

S: последний принятый бит - SТАRТ (I2C)

R/W: чтение/запись (действителен при совпадении адреса и до принятия битов SТАRТ, SТОР или АSК)

UA: обновить/нет адрес в регистре SSРАDD (10 разрядный I2C)

BF: буфер SSРВUF заполнен/пуст (при передаче - I2C). 1 - прием завершен/идет передача, 0 - идет прием/завершена передача.

Для передачи байта необходимо записать его в регистр SSРВUF. Во время приема информация записывается в регистр SSРSR и по его окончанию перемещается в регистр SSРВUF с одновременной установкой флага ВF. Запись в регистр SSРВUF во время осуществления передачи/приема игнорируется, однако при этом устанавливается бит WCOL сигнализирующий о коллизии. Для передачи следующего байта содержимое регистра SSРВUF должно быть прочитано, иначе не произойдет аппаратный сброс флага ВF и передача производится не будет.

2014-02-12

2014-02-12 533

533