Сумматором называется комбинационное логическое устройство, предназначенное для выполнения операции арифметического сложения чисел, представленных в виде двоичных кодов.

Сумматоры являются одним из основных узлов арифметико-логических устройств.

Различают полусумматоры и полные сумматоры. Полусумматором называется устройство, предназначенное для сложения двух одно разрядных кодов, которое имеет два входа и два выхода и формирующее из двух входных сигналов сигнал суммы и сигнал переноса в старший разряд. Ниже представлена таблица истинности полусумматора:

Таблица 4.5

| X1 | X0 | S | P |

В таблице 3.5 S – выходной сигнал суммы, P – выходной сигнал переноса.

На основании таблицы 3.4 составлена система логических уравнений полусумматора:

.

.

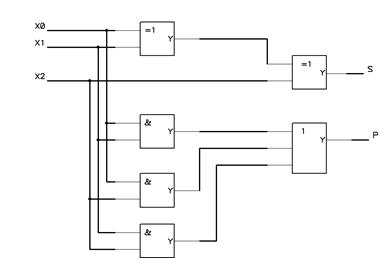

Для технической реализации полусумматора необходимы логические элементы И и исключающее ИЛИ.

При построении много разрядных сумматоров необходим полный сумматор. От полусумматора он отличается наличием третьего логического входа для сигнала переноса. Его работа описывается таблицей 4.6:

Таблица 4.6

| X2 | X1 | X0 | S | P |

или системой логических уравнений:

(31)

(31)

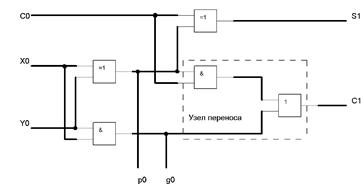

Вход Х2 служит для подачи сигнала переноса из предыдущего разряда. Возможная схема одно разрядного полного сумматора приведена на рис. 4.25.

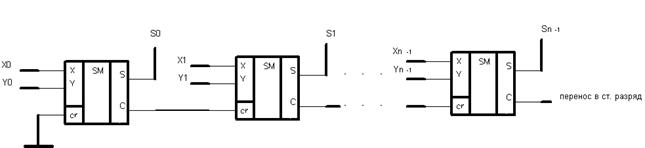

Сумматор для сложения n – разрядных двоичных чисел с последовательным переносом показан на рис. 4.26. Здесь “cr” обозначен вход переноса, а “C” - выход переноса. Основным недостатком много разрядных сумматоров, построенных по такой схеме, является большая задержка формирования переноса.

Рис. 4.25. Схема полного одноразрядного двоичного сумматора

Рассматривая схему рис. 4.26, можно заключить, что задержка переноса в одном разряде составляет  .

.

Рис. 4.26. Схема n- разрядного двоичного сумматора

Как видно из рис. 4.26, перенос распространяется последовательно по разрядам и общее время задержки составит:  . При этом в процессе установления сигнала на выходах сумматора ярко выражен эффект «гонок».

. При этом в процессе установления сигнала на выходах сумматора ярко выражен эффект «гонок».

Как было сказано в ЭВМ сумматоры являются одной из основных составляющих частей арифметико-логического устройства. Использование последовательной схемы переноса при сложении многоразрядных чисел приводит к возникновению недопустимо больших задержек и существенному снижению быстродействия ЭВМ. Поэтому были разработаны параллельные схемы формирования переноса. Используя тождество  , выражение для переноса Р в (30) можно преобразовать к следующему виду:

, выражение для переноса Р в (30) можно преобразовать к следующему виду:

, (32)

, (32)

Уравнению для суммы S из (31) с учетом уравнения для переноса соответствует схема рис. 4.27.

Рис. 4.27. Схема первого разряда сумматора

Узел, обведенный пунктирной линией называется узлом переноса, а сигналы р и g

и g – сигналами генерации переноса и распространения переноса соответственно.

– сигналами генерации переноса и распространения переноса соответственно.

Рассматривая рис. 4.26 и 4.27, можно записать:

(33)

(33)

...

Технически реализуя уравнения (33) получают схему ускоренного переноса (узел переноса), где задержка переноса не превышает  не зависимо от числа разрядов сумматора. Причем узел переноса усложняется от разряда к разряду.

не зависимо от числа разрядов сумматора. Причем узел переноса усложняется от разряда к разряду.

В качестве примера на рис. 4.28 представлено условное графическое обозначение на схеме электрической принципиальной микросхемы полного четырехразрядного сумматора К155ИМ3.

Кроме рассмотренных сложных микросхем комбинационной логики промышленность выпускает множество других типов, например схемы сравнения кодов, схемы проверки четности, арифметико-логические устройства и т. д.

Рис. 4.28. Полный четырехразрядный сумматор К155ИМ3

2014-02-13

2014-02-13 1823

1823