В аналого-цифровом преобразователе (АЦП) выключите антиэлайсинговый ФНЧ (на входе схемы выборки-хранения (СВХ)). Установите разрядность АЦП N = 8, тип логики поразрядного уравновешивания «2». Выберите в качестве передаваемого сигнала колокольный импульс (№ 5 от источника сигнала) при его длительности 10 мс. Масштаб развертки осциллографа установите 0 – 7,5 мс (кнопкой «t x 2»).

Наблюдайте и зафиксируйте осциллограммы и спектрограммы сигналов в разных точках СПНС в следующем порядке по каналам:

1) передаваемый сигнал на входе АЦП (т.13),

2) на выходе СВХ (т.15),

3) на выходе АЦП (т.18),

4) на выходе модулятора (АМ) (т.4).

Комментарии и выводы

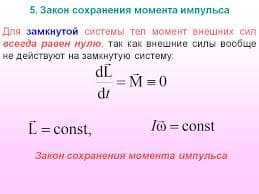

Для передачи аналоговых сигналов по цифровому каналу их предварительно преобразуют в цифровой поток с помощью аналого-цифрового преобразователя (АЦП).

Работа АЦП с поразрядной логикой уравновешивания протекает следующим образом:

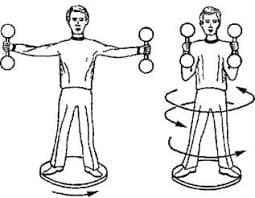

1) Преобразуемое аналоговое напряжение подвергается дискретизации в схеме выборки-хранения (СВХ) для хранения отсчетов ui в течении цикла преобразования (периода цикловых импульсов (ЦИ)).

2) Компаратор сравнивает эти отсчеты с напряжением от генератора образцовых напряжений (ГОН) u ГОН.

3) В качестве ГОН используется цифро-аналоговый преобразователь (ЦАП) на вход которого подается последовательность кодов от схемы логики поразрядного уравновешивания. Эти коды с помощью ЦАП преобразуются в ступенчатое образцовое напряжение u ГОН, начинающееся со среднего значения диапазона преобразования АЦП Δ.

На первом такте по реакции компаратора определяется, в какой половине Δ лежит отсчет ui. Если ui > u ГОН, то отсчёт в верхней половине Δ и старший разряд двоичного числового эквивалента отсчета равен 1, иначе – в нижней половине Δ и старший разряд – 0. Для второго такта устанавливается образцовое напряжение, соответствующее середине выявленной половины диапазона (0,75Δ при ui > u ГОН и 0,25Δ при ui < u ГОН).

На каждом последующем такте эта процедура повторяется, и определяются шаг за шагом все N разрядов цифрового значения отсчета ui, начиная со старшего. Получаемые значения разрядов цифрового отсчета можно сразу выводить на выход АЦП без дополнительной задержки на длительность цикла преобразования, как это имеет место при использовании логики последовательного уравновешивания.

Нетрудно сообразить, что частота следования ТИ должна в N раз превышать частоту ЦИ (N – разрядность АЦП), а шаг квантования в 2 N раз меньше диапазона преобразования АЦП. По этой причине поразрядная логика уравновешивания работает в 2 N / N раз быстрее последовательной.

С выхода АЦП цифровые отсчета сигнала в последовательном формате поступают на вход модулятора (если не используется канальное помехоустойчивое кодирование, как в данном случае) для дальнейшей передачи по каналу связи.

2015-01-21

2015-01-21 366

366