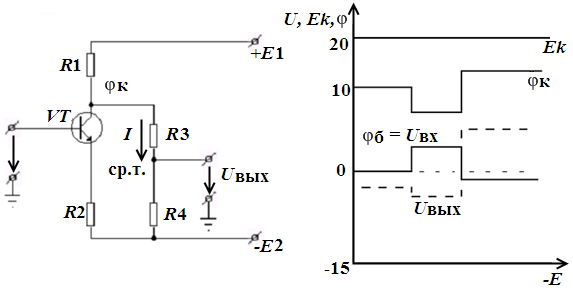

Рассмотрим схему такого однокаскадного усилителя (рисунок 2.33), в нем применены 2 источника питания + Е 1 и – Е 2, которые создают «+» и «−» напряжение относительно общей точки, имеющей нулевой потенциал («земля»). Входной сигнал подается непосредственно на базу транзистора.

| Рисунок 2.33 – УПТ с двумя источниками питания и его потенциальная диаграмма |

При U вх = 0, потенциал базы φб = 0. Потенциалы других точек схемы (относительно общей точки) зависят от напряжений источников питания. К делителю R 3 / R 4, в отсутствии входного сигнала, приложено напряжение φ R 3 + φ R 4 = φк - (- E 2) = φк + E 2, при этом потенциал средней точки делителя должен быть равен нулю, т. е. напряжение на выходе равно 0, при этом падение напряжение на плечах делителя соответственно равны UR 3 = φк, UR 4 = E 2. Чтобы ток делителя не нарушал режима работы транзистора, его обычно выбирают значительно меньше I к:

При U вх = 0, потенциал базы φб = 0. Потенциалы других точек схемы (относительно общей точки) зависят от напряжений источников питания. К делителю R 3 / R 4, в отсутствии входного сигнала, приложено напряжение φ R 3 + φ R 4 = φк - (- E 2) = φк + E 2, при этом потенциал средней точки делителя должен быть равен нулю, т. е. напряжение на выходе равно 0, при этом падение напряжение на плечах делителя соответственно равны UR 3 = φк, UR 4 = E 2. Чтобы ток делителя не нарушал режима работы транзистора, его обычно выбирают значительно меньше I к: I = (0,02 − 0,1) I к.

Сопротивление резисторов делителя могут быть определены из соотношений:

R 3 = UR 3 / I

R 4 = UR 4 / I

При подаче входного напряжения (положительной полярности) возрастает ток базы транзистора I б, что приводит к увеличению коллекторного тока I к. При этом увеличивается падение напряжения на R 1 и снижается потенциал верхнего вывода делителя R 3 / R 4, снижается потенциал средней точки делителя и на выходе появляется напряжение отрицательной полярности. Таким образом, делитель R 3 / R 4 компенсирует const составляющую напряжения и передает с некоторым уменьшением усиленное напряжение с коллектора транзистора на выход усилителя.

Коэффициент усиления такого усилительного каскада при R3 >> R1 и R4 >> R1, когда шунтирующие действия делителя можно не учитывать, определяется выражением:

K = K 0 · (R 4 / (R 3 + R 4)),

где K 0 – коэффициент усилителя с коллекторной нагрузкой без делителя;

R 4 / (R 3 + R 4) – множитель, учитывающий снижение коэффициента усиления за счет включения делителя.

Дрейф в УПТ

УПТ имеют один недостаток, затрудняющий усиление очень малых постоянных напряжений и токов. В УПТ существует так называемый дрейф нуля, который определяет нижний предел усиливаемых напряжений. Дрейф нуля заключается в следующем. С течением времени изменяются токи транзисторов и напряжения на их электродах. При этом нарушается компенсация постоянной составляющей напряжения и на выходе усилителя появляется напряжение в отсутствие входного сигнала. Т. к. УПТ должен усиливать напряжения вплоть до самых низких частот, всякое изменение постоянных составляющих напряжения U к0, U б0 из-за:

- нестабильности источников питания;

- старения транзисторов;

- изменения температуры окружающей среды и т. д.;

- принципиально не отличается от полезного сигнала.

Если вход УПТ замкнуть накоротко, а на входе подключить милливольтметр, то с течение времени даже при отсутствии входного напряжения из-за нестабильности величины U к0 и U б0 и неточной их компенсации появляется выходное напряжение.

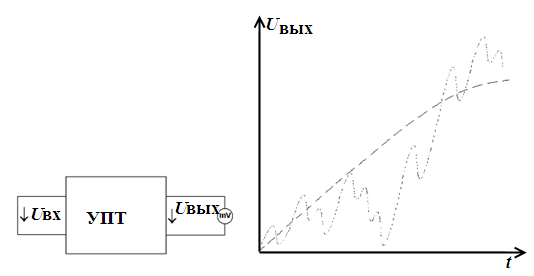

Примерная временная зависимость U вых показана на графике (рисунок 2.34). Это напряжение, деленное на коэффициент усиления усилителя, называют дрейфом нуля, приведенным к входу усилителя:

Примерная временная зависимость U вых показана на графике (рисунок 2.34). Это напряжение, деленное на коэффициент усиления усилителя, называют дрейфом нуля, приведенным к входу усилителя:

U др = U вых / K u (при U вх = 0).

| Рисунок 2.34 – Дрейф нуля в УПТ |

Как видно из временной зависимости, U вых состоит как бы из 2-х составляющих:

- монотонно изменяющегося напряжения (штриховая линия);

- переменной составляющей.

Для борьбы с дрейфом нуля принимают целый ряд мер:

- стабилизацию напряжения источников питания;

– стабилизацию температурного режима и тренировку транзисторов;

– использование дифференциальных (или балансных) схем УПТ;

- преобразование усиливаемого напряжения.

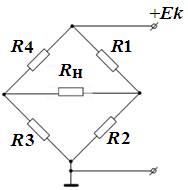

Для борьбы с дрейфом в УПТ применяют специальные схемы усилителей, которые называются дифференциальными или балансными. Такие схемы построены по принципу четырехплечевого моста (рисунок 2.35).

| Рисунок 2.35 – Схема четырехплечевого моста |

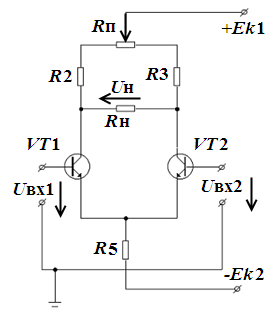

Если мост сбалансирован, т. е. R 1 / R 2 = R 4 / R 3, то при изменении напряжения источника питания + Е к баланс не нарушается и в нагрузочном резисторе R н ток равен нулю. С другой стороны, при пропорциональном изменении сопротивлений резисторов R 1, R 2 или R 3, R 4 баланс моста тоже не нарушается. Если заменить резисторы R 2, R 3 транзисторами, то получим дифференциальную схему, часто применяемую в УПТ (рисунок 2.36).

Если мост сбалансирован, т. е. R 1 / R 2 = R 4 / R 3, то при изменении напряжения источника питания + Е к баланс не нарушается и в нагрузочном резисторе R н ток равен нулю. С другой стороны, при пропорциональном изменении сопротивлений резисторов R 1, R 2 или R 3, R 4 баланс моста тоже не нарушается. Если заменить резисторы R 2, R 3 транзисторами, то получим дифференциальную схему, часто применяемую в УПТ (рисунок 2.36). Назначение элементов схемы:

-

| Рисунок 2.36 – Дифференциальная схема в УПТ |

R 1 стабилизирует ток транзисторов, включен в эмиттерную цепь обоих транзисторов; чтобы можно было использовать резистор с большим сопротивлением R 1, увеличивают напряжение источника питания Е к до значения Е к2 = Е к1, а в интегральных микросхемах вместо R1 применяют стабилизатор постоянного тока, который выполняют на 2-х транзисторах.

R 1 стабилизирует ток транзисторов, включен в эмиттерную цепь обоих транзисторов; чтобы можно было использовать резистор с большим сопротивлением R 1, увеличивают напряжение источника питания Е к до значения Е к2 = Е к1, а в интегральных микросхемах вместо R1 применяют стабилизатор постоянного тока, который выполняют на 2-х транзисторах. - переменный резистор R п служит для установки нуля. Это необходимо в связи с тем, что не удается подобрать два абсолютно идентичных транзистора и резисторы с равными сопротивлениями R 2, R 3. При изменении положения движка потенциометра R п изменяются сопротивления резисторов, включенных в коллекторные цепи транзисторов и, следовательно, потенциалы на коллекторах. Перемещением движка потенциометра R п добиваются нулевого тока в нагрузочном резисторе R н при отсутствии входного сигнала.

При изменении э.д.с. источника коллекторного питания Е 1 или смещения Е 2 изменяются токи обоих транзисторов и потенциалы их коллекторов. Если транзисторы идентичны и сопротивления R 2, R 3 в точности равны, то тока в резисторе R н за счет изменения э.д.с. Е 1, Е 2 не будет. Если транзисторы не совсем идентичны, то появляется ток в нагрузочном резисторе, однако он будет значительно меньше, чем в обычном, небалансном УПТ.

При подаче входного сигнала на базу транзистора VТ 1, увеличивается ток базы транзистора VТ 1 и уменьшится ток базы транзистора VТ 2. При этом токи I э1, I к1 увеличиваются, а токи I э2, I к2 уменьшаются. Изменение токов происходит на одну и ту же величину. Напряжение U к1 = E к1 − I к1 R к1 100 уменьшается, что вызывает приращение напряжения – ∆ U к1, противоположное по знаку (т. е. проинвертированное) U вх. Напряжение U к2 = E к1 − I к2 R к2 возрастает, что создает приращение напряжения того же знака + ∆ U k2 (т. е. непроинвертированное), что и напряжение входного сигнала. Т. е. в данном случае выход каскада со стороны коллектора транзистора VТ 1 является инвертирующим, а со стороны коллектора транзистора VT 2-неинвертирующим. Если подает сигнал на вход VТ 2, то тогда коллектор транзистора VТ 2 будет инвертирующим выходом, а коллектор VТ 1-неинвертирующим.

Если напряжение подается на оба входа сразу, то инвертирующий и неинвертирующий выходы (или входы) определяются на сравнении по формуле U вых = K (U вх1 − U вх2).

2015-02-27

2015-02-27 2824

2824