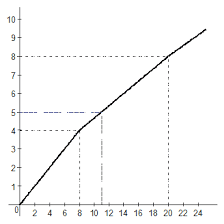

Схемотехническую реализацию ПЗУ масочного типа иллюстрирует рис. 7.2. Схема имеет адресные входы х 1, х 2, выходы содержимого ячеек памяти z 1 –z 4, вывод для подключения источника питания Е и общий вывод. Верхняя часть схемы представляет собой полный дешифратор. Если разрядность адреса равна n, то в дешифраторе имеем 2 n горизонтальных входных линий, на которых формируются входные переменные и их инверсии. Число вертикальных линий в полном дешифраторе равно 2 n. С помощью специальных масок программируется наличие или отсутствие р-n -перехода в цепи связи вертикальных и горизонтальных шин матрицы. Размещение диодов матрицы Ипоказано на рисунке жирными точками. Диоды ориентированы так, как показано на вынесенной в кружок части рисунка.

На вертикальных шинах матрицы реализуются логические функции  . Каждому набору входных переменных, т. е. адресу ПЗУ, соответствует уровень логической единицы на одной из вертикальных линий и логического 0 на всех остальных. Диоды дешифратора реализуют матрицу И.

. Каждому набору входных переменных, т. е. адресу ПЗУ, соответствует уровень логической единицы на одной из вертикальных линий и логического 0 на всех остальных. Диоды дешифратора реализуют матрицу И.

В нижней части рисунка диоды реализуют матрицу ИЛИ. Количество горизонтальных линий соответствует разрядности слова, записанного по каждому адресу. Наличие диода формирует 1 в соответствующем бите выходного слова, отсутствие диода — 0. В ПЗУ схема дешифратора неизменна, а программируется матрица связей ИЛИ (они удобны для реализации преобразователей кода).

В ПЛМ(программируемых логических матрицах) программируются обе матрицы (Ии ИЛИ). ПЛМ удобны для реализации сложных логических функций, их преимущества особенно заметны при большом числе входных переменных.

В данном примере реализовано ПЗУ, карта прошивки которого представлена ниже в таблице, слева от которой записаны реализуемые логические функции.

,

,

,

,

,

,

.

.

2015-02-18

2015-02-18 941

941