Таблица переходов и логическое уравнения D-триггера

Триггером типа D называется синхронный запоминающий элемент с двумя устойчивыми состояниями и одним информационным D-входом.

Закон функционирования D-триггера описывается логическим уравнением:

Qt+1 = Ct Dt

Это уравнение показывает, что после переключения состояние D-триггера повторяет значение сигнала на D-входе в тактовые моменты времени.

Поэтому в литературе D-триггеры часто называют триггерами задержки (от Delay— задержка).

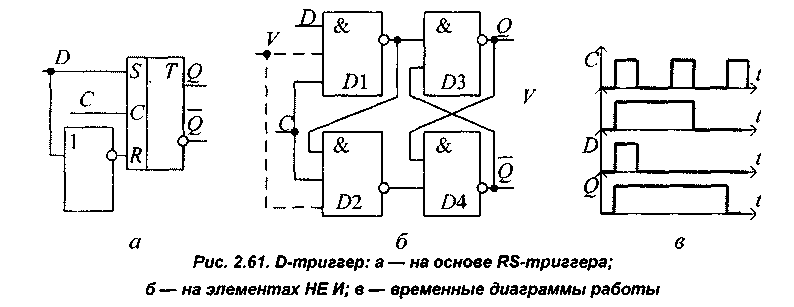

Схему D-триггера можно построить на основе синхронного RS-триггера, если сигнал по входу S одновременно подавать через инвертор на вход R (рис. 4.39, а).

Схемы D-триггера строят также на основе самостоятельного логического уравнения. Преобразуем уравнение (4.5) путем замены сигнала S на D и сигнала R на D:

Qt+1 = C ∙S ∙C ∙R ∙Q = C ∙D ∙C ∙D ∙Q (4.11)

Схема D-триггера на элементах НЕ-И с логическими связями согласно уравнению (4.11) показана на рис. 4.39, б.

Рисунок 4.39 – D-триггер:

а –на основе RS-триггера; б -на элементах НЕ-И; в –временные диаграммы работы

D-триггер "следит" за изменением сигнала на D-входе во время действия синхросигнала С и сохраняет ту информацию, которая имелась в момент его окончания.

RS-триггеры таким свойством не обладают и потому они менее помехозащищенные в сравнении с D-триггерами.

Для задержки информации в D-триггере на произвольное число тактов используется разрешающий V-вход, как показано штриховой линией на рис. 4.39, б.

Если V = 1, то DV-триггер функционирует как обычный триггер задержки;

Если V = 0, то работа схемы по входам блокируется и D-триггер сохраняет предыдущую информацию.

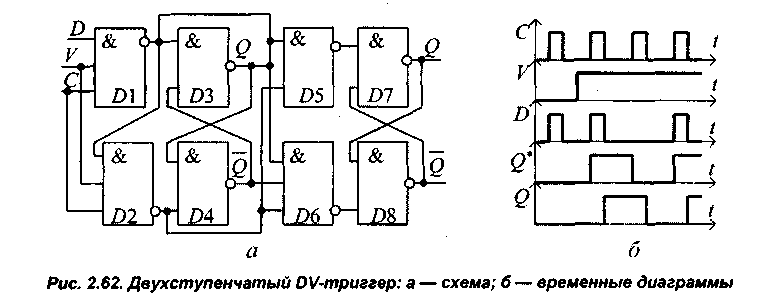

Схема двухступенчатого однотактного DV-триггера на элементах НЕ-И с запрещающими связями между ступенями показана на рис. 4.40.

Рисунок 4.40 –Двухступенчатый DV-триггер:

а –схема; б –временные диаграммы работы

2015-03-22

2015-03-22 4075

4075