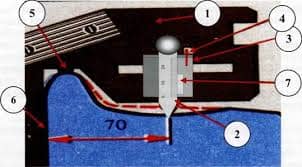

Для организации параллельного переноса применяются специальные узлы — блоки ускоренного переноса.

Принцип ускоренного переноса заключается в том, что для каждого двоичного разряда дополнительно находятся два сигнала:

G — образование переноса и H — распространение переноса.

GI = aI·bI

HI = aI + bI

В случае GI =1, то есть aI=bI =1, в данном i-разряде формируется сигнал переноса PI +1 в следующий высший разряд независимо от формирования функций суммы в предыдущих разрядах.

Если хотя бы одно из слагаемых aI или bI равно «1», то есть HI =1, то перенос в последующий разряд производится при наличии сигнала переноса из предыдущего разряда.

Если HI=HI –1=1 и при этом существует сигнал переноса PI из предыдущего в i-й разряд, то перенос производится сразу в i+2 разряд.

В общем случае процесс формирования ускоренного переноса описывается следующим уравнением:

PI +1 = GI + HI · GI –1 + HI · HI –1· GI –2 + … + HI · HI –1·…· H 2· H 1· P 1

Блоки ускоренного переноса выпускаются в интегральном исполнении в виде отдельных микросхем или непосредственно со схемой сумматора или арифметико-логического устройства в одной микросхеме.

ЛЕКЦИЯ 20

2015-05-05

2015-05-05 697

697