Логическое моделирование (симуляция) проекта дает возможность проверить логику работы схемы устройства с помощью временных диаграмм. Следует помнить, что временные диаграммы не учитывают задержку прохождения сигнала в устройстве и необходимы лишь для проверки правильности работы устройства.

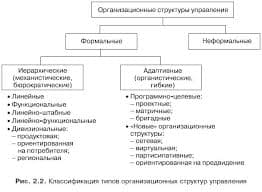

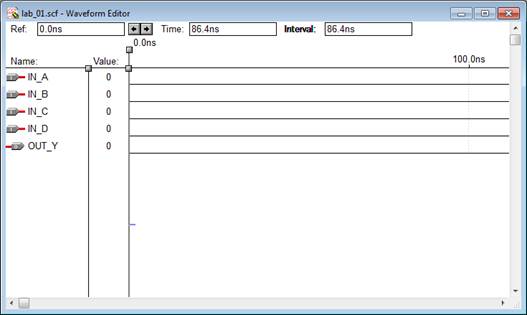

Создание файла сигнального редактора. Для создания файла сигнального редактора необходимо в окне создания нового файла, в поле выбора типа файла («File Type») выбрать пункт «Waveform Editor File». После чего появится окно сигнального редактора («Waveform Editor») (рис. 22).

Рисунок 22. Окно сигнального редактора.

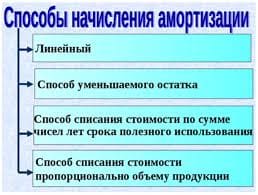

Добавление входов и выходов схемы. Для добавления сигнала необходимо:

1) Правой клавишей мыши щёлкнуть по пустому месту сигнального редактора и выбрать пункт «Insert Node», либо дважды кликнуть левой кнопкой мыши в поле «Name»;

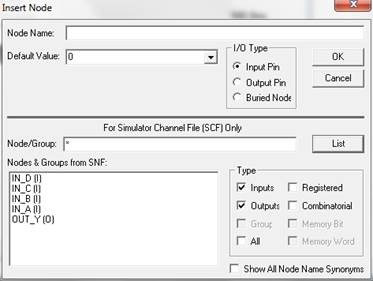

2) В появившемся окне (рис. 23) нажать кнопку «List»;

3) Из появившегося списка в поле «Nodes & Groups from SNF» выбрать вход (выход) и нажать «ОК»;

Рисунок 23. Добавление сигнала.

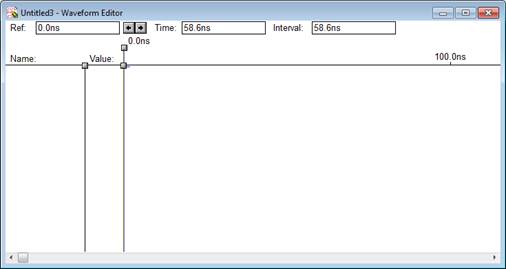

4) Повторить операции 1-3 для остальных входов и выходов. В результате окно сигнального редактора должно выглядеть как на рисунке 24.

Рисунок 24. Исследуемые сигналы.

Установка размера сетки и её отображения. Для настройки параметров сетки необходимо:

1) Выбрать пункт «Grid Size…» из меню «Options»;

2) В появившемся окне установить значение 5ns, что соответствует 5 наносекундам;

3) Нажать кнопку «ОК»;

4) Если необходимо (если сетка не отображается) включить сетку путём выбора пункта «Show Grid» в меню «Options».

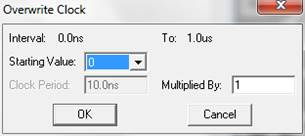

Задание входных сигналов. Для задания входного сигнала щелкните правой кнопкой мыши по названию входа в поле «Name» и в контекстном меню выбрать пункт «Overwrite->Clock…». В появившемся окне (рис. 25) оставить «начальное значение» («Starting Value») равным 0, а «множитель» («Multiplied By») установить равным 1.

Рисунок 25. Окно задания параметров.

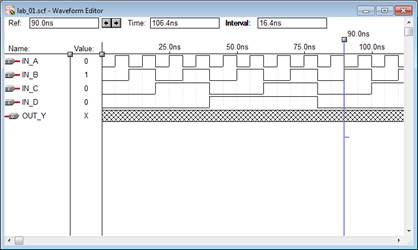

Повторить эти действия, удваивая каждый раз множитель, для остальных входных сигналов. Данная конфигурация входных сигналов представляет собой таблицу истинности схемы, только в графическом виде. Для выходного сигнала (для наглядности) можно установить «неизвестный логический уровень» («undefined (X) logic level») В результате окно сигнального редактора должно выглядеть как на рисунке 26.

Рисунок 26. Форма входных сигналов.

Проверка и сохранение файла сигнального редактора. Для проверки файла на ошибки и сохранения необходимо вызвать пункт меню «File->Project->Save & Check».

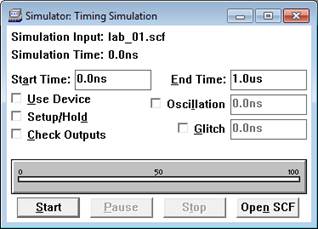

Запуск симуляции. Для запуска симуляции необходимо выбрать пункт «Simulator» в меню «MAX+plus II». В появившемся окне (рис. 27) нажать кнопку «Start».

Рисунок 27. Окно симулятора.

По окончании симуляции появится сообщение о завершении симуляции, в котором будет указано количество ошибок и предупреждений. Нажмите «ОК».

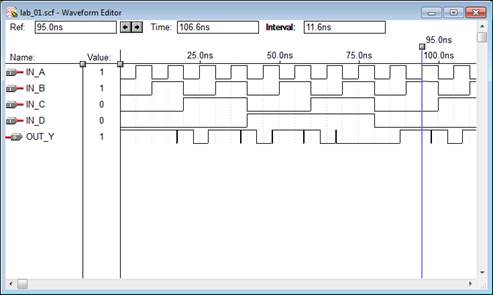

Выходной сигнал в окне сигнального редактора изменился и должен выглядеть, как показано на рисунке 28.

Рисунок 28. Результаты функционального моделирования.

Проверить полученный результат, можно составив таблицу истинности схемы и сравнив ее с результатом моделирования.

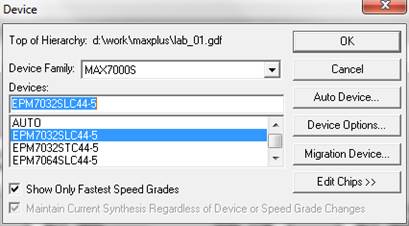

Выбор семейства ПЛИС. Для выбора семейства ПЛИС необходимо:

1) Выбрать пункт «Device» в меню «Assign», после чего откроется окно выбора семейства ПЛИС (рис. 29)

Рисунок 29. Окно выбора семейства ПЛИС.

2) В окне выбора ПЛИС можно задать семейства используемых микросхем, а затем и определиться с конкретной микросхемой, после чего нужно нажать кнопку «ОК». В случае, когда конкретная марка ПЛИС не важна – можно установить выбор ПЛИС в положение «Auto», тогда программа в автоматическом режиме выберет соответствующую микросхему.

После выбора ПЛИС необходимо снова откомпилировать проект («File->Project->Save & Compile»).

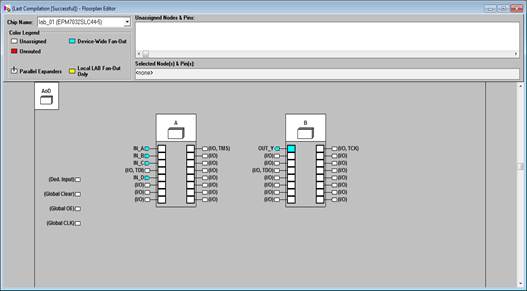

4.7 Редактор базового плана кристалла

Редактор базового плана кристалла вызывается соответствующим пунктом меню («Floorplan Editor») в главном меню программы («MAX+plus II»).

В окне редактора автоматически откроется план микросхемы, выбранной на этапе компиляции (рис. 30).

Примечание: План микросхемы откроется только в том случае, если была выбрана конкретная ПЛИС, а не AUTO.

Рисунок 30. Окно редактора базового плана кристалла.

2015-05-10

2015-05-10 546

546