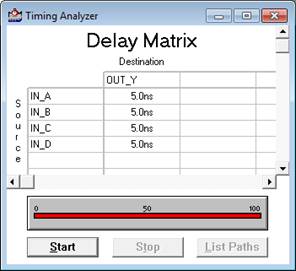

Временной анализ показывает время прохождения сигнала от входа к выходу. Для его вызова необходимо выбрать пункт «Timing Analyzer» в меню «MAX+plus II» и в появившемся окне нажать «Start». По завершению появится сообщение о результатах временного анализа. Результаты будут представлены в окне «Timing Analyzer» (рис. 31).

Рисунок 31. Окно временного анализа.

ВАРИАНТЫ ЗАДАНИЙ

Для моделирования схем необходимо подать на входы сигналы, меняющиеся по таблице истинности.

В схемах вариантов 14 и 15 на входы синхронизации (IN_C и NC, соответственно) подается низкий логический уровень (0).

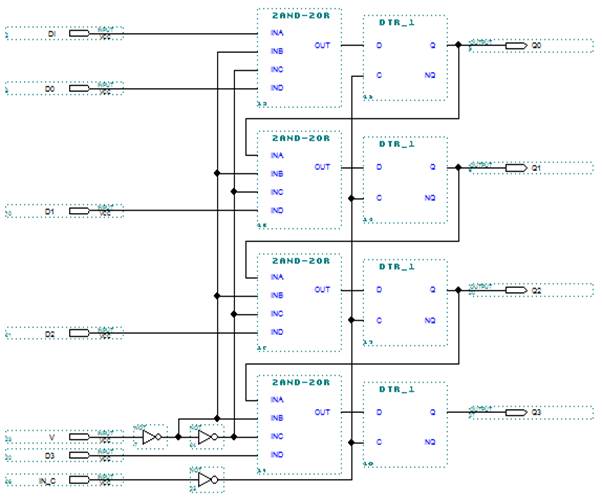

В схеме варианта 14, при подаче на вход V высокого логического уровня, универсальный регистр будет работать как параллельный регистр. В этом режиме входные сигналы подаются на входы D0 – D3. При подаче на вход V низкого логического уровня, регистр будет работать как последовательный. Входной сигнал в таком режиме подается на вход DI.

В схеме варианта 15, входы A0 и A1 – адресные входы. При подаче стробирующего сигнала на вход NС мультиплексор выбирает один из входов, адрес которого задается двоичным кодом на адресных входах, и подключает его к выходу. Например, если адресные входы содержат адрес 01, соответствующий 1 в десятичной системе, то на выход будет подаваться сигнал с первого входа (D1). Для моделирования данной схемы необходимо подать на адресные входы какой-нибудь сигнал (например, 00), на входы D0-D3 подать сигнал по таблице истинности и запустить симуляцию. После чего необходимо подать на адресные входы другой сигнал (например, 10) и снова провести симуляцию (сигналы на входах D0-D3 оставить без изменений). Сравнить оба результата и сделать вывод.

Вариант №1

Рисунок 3.5 – Параллельный регистр

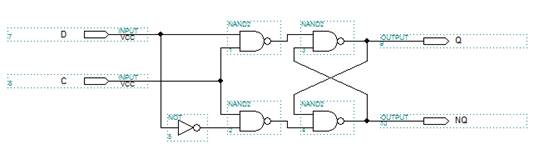

Рисунок 3.6 – D-триггер

Вариант №2

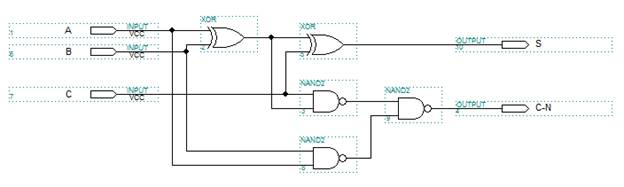

Рисунок 3.7 – Трехразрядный сумматор на элементах исключающее ИЛИ, И-НЕ

Рисунок 3.8 – Сумматор на элементах исключающее ИЛИ, И-НЕ

Вариант №3

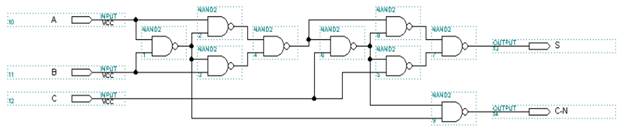

Рисунок 3.9 – Трехразрядный сумматор на элементах И-НЕ

Рисунок 3.10 – Сумматор на элементах И-НЕ

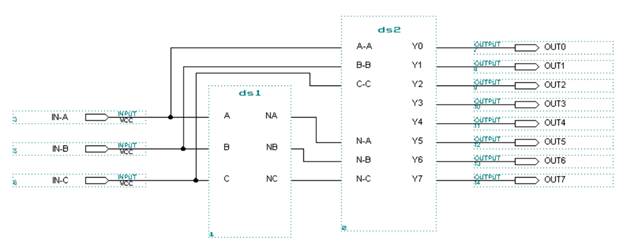

Вариант №4

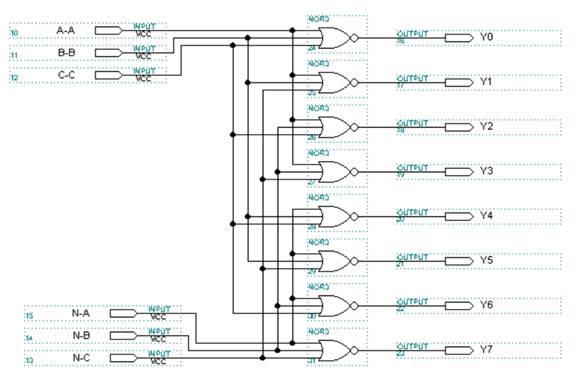

Рисунок 3.11 – Дешифратор на элементах И-НЕ

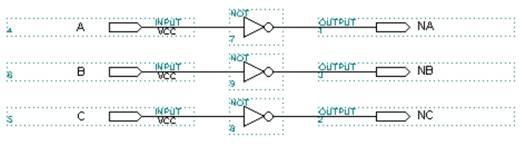

Рисунок 3.12 – Блок ds1

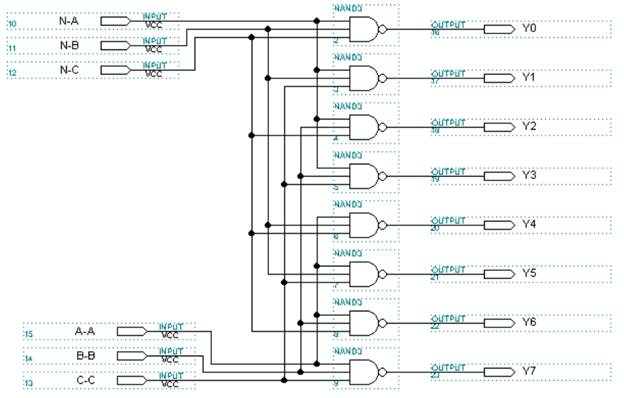

Рисунок 3.13 – Блок ds2

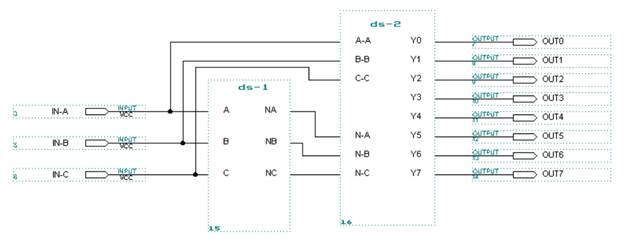

Вариант №5

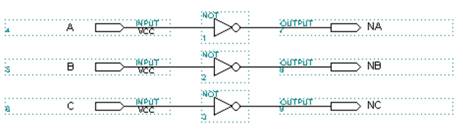

Рисунок 3.14 – Дешифратор на элементах ИЛИ-НЕ

Рисунок 3.15 – Блок ds1

Рисунок 3.16 – Блок ds2

Вариант №6

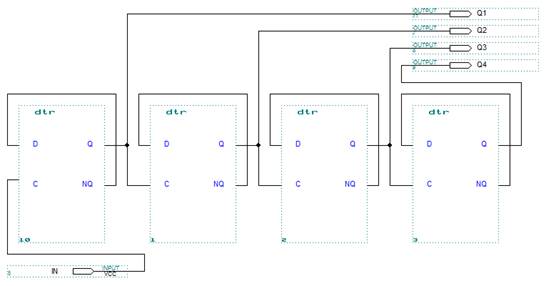

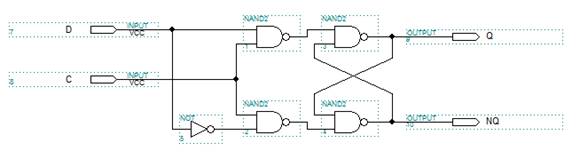

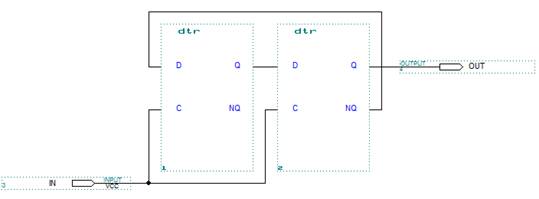

Рисунок 3.17 – Последовательный регистр

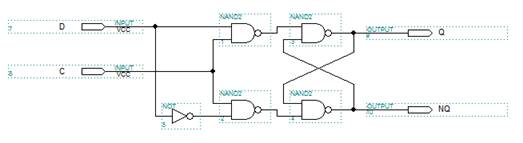

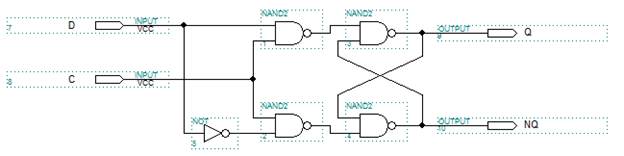

Рисунок 3.18 – D-триггер

Вариант №7

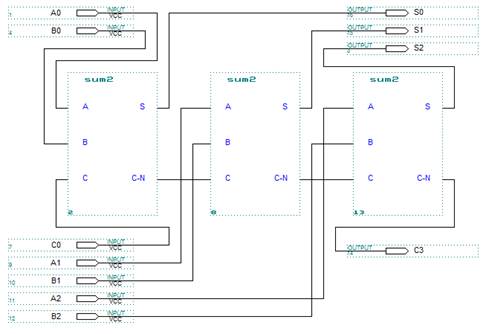

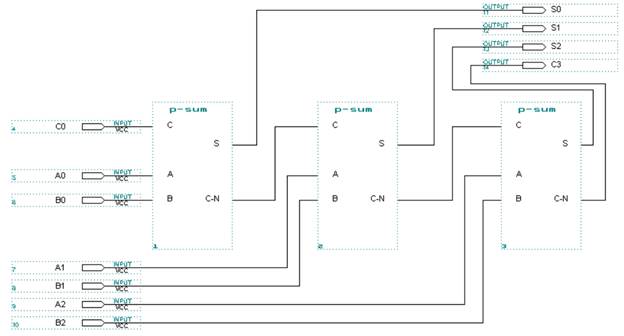

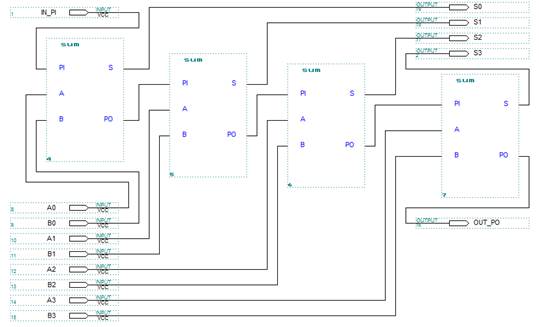

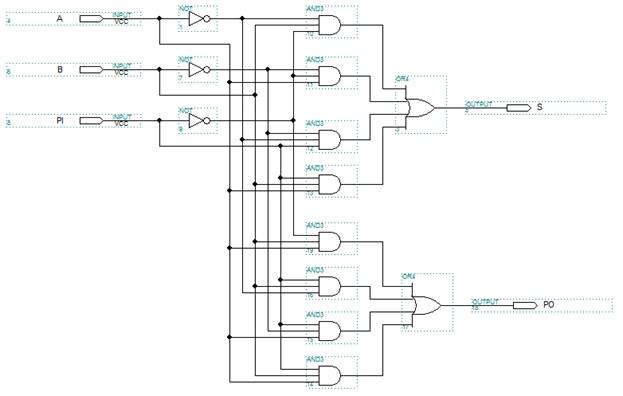

Рисунок 3.19 – Многоразрядный двоичный сумматор

Рисунок 3.20 – Двоичный одноразрядный сумматор

Вариант №8

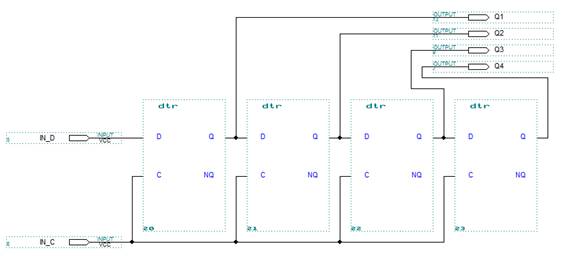

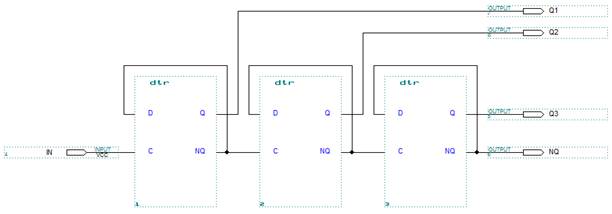

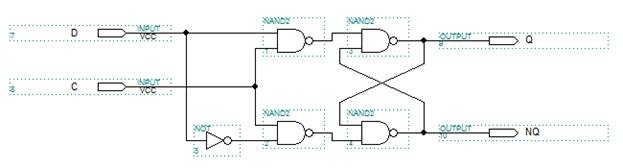

Рисунок 3.21 – Счетчик

Рисунок 3.22 – D-триггер

Вариант №9

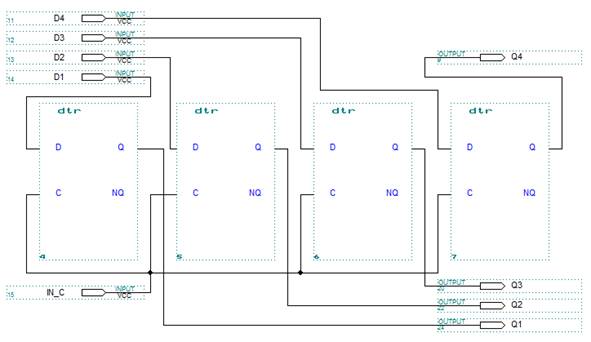

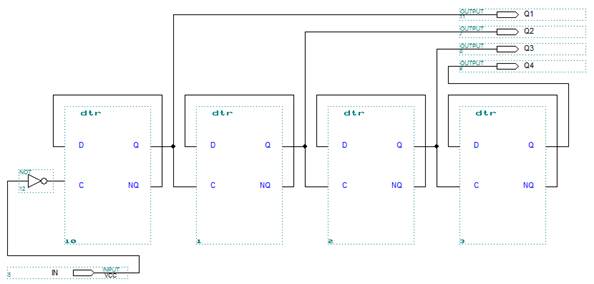

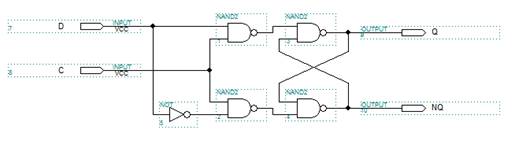

Рисунок 3.23 – Четырехразрядный счетчик на универсальных D-триггерах

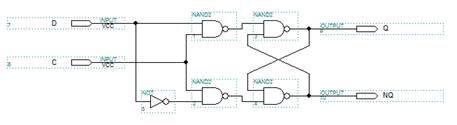

Рисунок 3.24 – D-триггер

Вариант №10

Рисунок 3.25 – Четырехразрядный двоичный вычитающий счетчик на универсальных D-триггерах

Рисунок 3.26 – D-триггер

Вариант №11

Рисунок 3.27 – Кольцевой счетчик

Рисунок 3.28 – D-триггер

Вариант №12

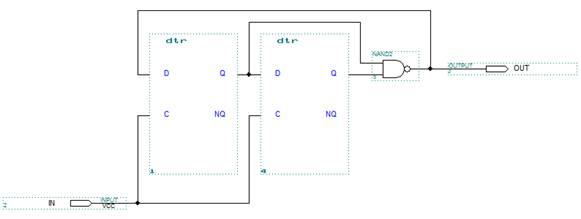

Рисунок 3.29 – 2-разрядный счетчик с проверкой правильности работы

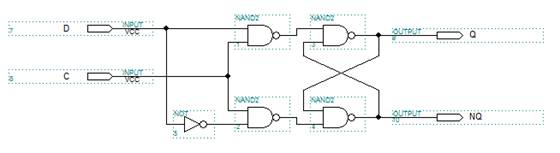

Рисунок 3.30 – D-триггер

Вариант №13

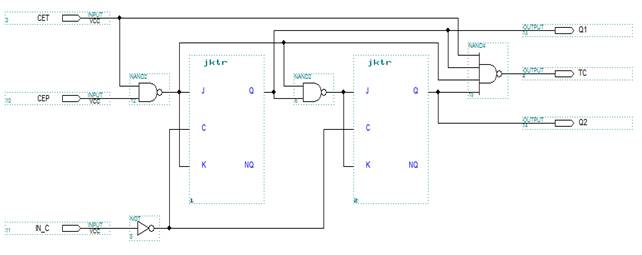

Рисунок 3.31 – 2-разрядный синхронный двоичный счетчик

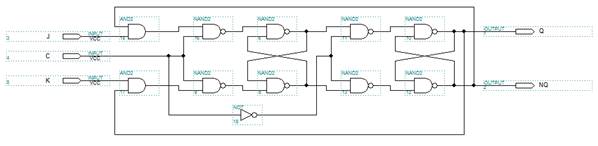

Рисунок 3.32 – JK-триггер

Вариант №14

Рисунок 3.33 – Универсальный регистр

Рисунок 3.34 – D-триггер

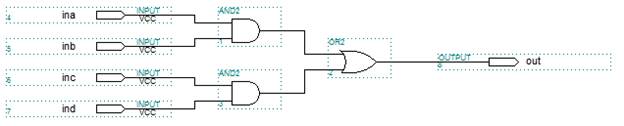

Рисунок 3.35 – Коммутатор (2-2И-2ИЛИ)

Вариант №15

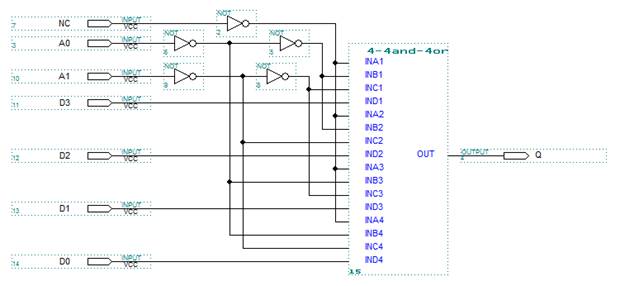

Рисунок 3.36 – Мультиплексор с четырьмя информационными входами

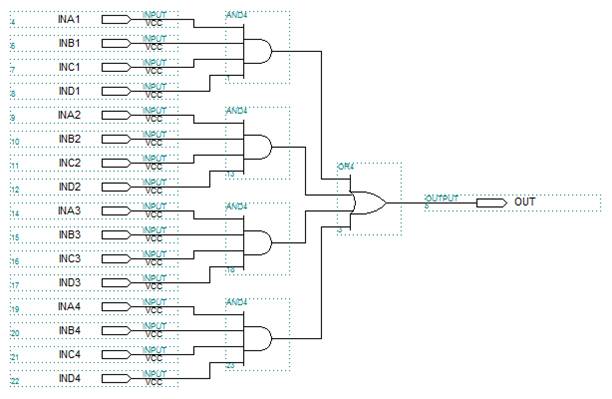

Рисунок 3.37 – Коммутатор (4-4И-4ИЛИ)

КОНТРОЛЬНЫЕ ВОПРОСЫ

6.1 Контрольные вопросы по теме «Конструктивно-технологические особенности ПЛИС»:

1) Конструктивно-технологические особенности ПЛИС?

2) На какие виды (по архитектуре) классифицируются ПЛИС?

3) Существуют ли альтернативные способы реализации специализированных микросхем?

4) Какие недостатки имеют ПЛИС по сравнению с заказными СБИС?

5) Какие преимущества имеют ПЛИС по сравнению с заказными СБИС?

6) Чем отличаются «системы на программируемом кристалле» от ПЛИС?

7) Каким образом программируются ПЛИС? Что такое теневая память?

8) В чем заключается особенность комбинированных ПЛИС?

9) Чем отличаются ПМЛ от ПЛМ?

10) Способы задания конфигурации в однократно программируемых ПЛИС?

6.2 Контрольные вопросы по теме «Интегрированная среда разработки MAX+Plus II»:

1) Конструктивно-технологические особенности ПЛИС?

2) Для чего нужны САПР?

3) Какие САПР выпускает фирма ALTERA?

4) Каковы преимущества Quartus II?

5) Перечислите основные этапы проектирования специализированных микросхем.

6) Какие существуют способы ввода описания проекта в среде проектирования?

7) Для чего используется символ схемы?

8) Какими преимуществами обладает текстовый редактор?

9) Для чего используется сигнальный редактор?

10) В чем заключается особенность логического моделирования?

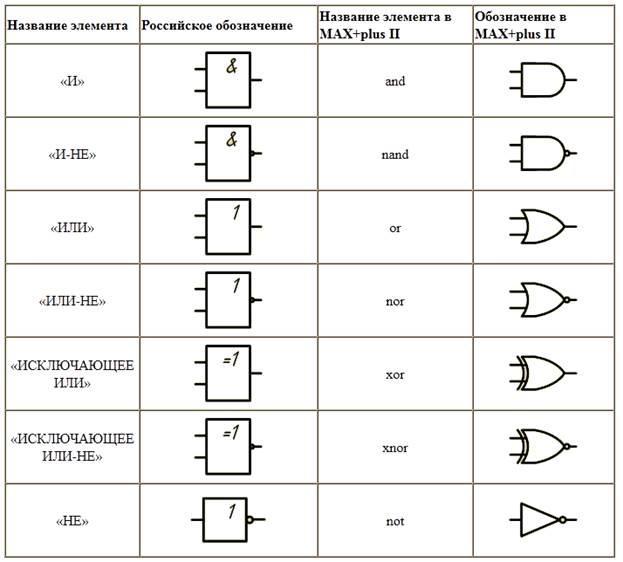

ПРИЛОЖЕНИЕ

Таблица 2. Соответствия российских обозначений элементов и обозначений в MAX+plus II.

ЛИТЕРАТУРА

1. Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы.- М.:Радио и связь. 1994 - 240 с

2. Бутаев М.М., Вашкевич Н.П., Гурин Е.И., Коннов Н.Н. Проектирование цифровых устройств на программируемых логических интегральных схемах: Учебн. пособие. - Пенза: Изд-во Пенз. гос. техн. ун-та, 1996.

3. Стешенко В. Б. Школа разработки аппаратуры цифровой обработки сигналов на ПЛИС // Chip News. 1999. № 8 – № 10. 2000. № 1 – № 3.

4. Стешенко В. Б. ПЛИС фирмы ALTERA: элементная база, система проектирования и языки описания аппаратуры. 3-е издание стереотипное. – Москва: Издательский дом «Додэка-XXI», 2007.

5. Максфилд К. Проектирование на ПЛИС. Архитектура, средства и методы. Курс молодого бойца. – Москва: Издательский дом «Додэка-XXI», 2007.

6. Грушвицкий Р.И., Мурсаев А. Х., Угрюмов Е.П. Проектирование систем на микросхемах программируемой логики. – БВХ-Петербугр, 2002.

7. Публикации фирмы Altera // http://altera.com/literature/lit-index.html

8. Представительство Altera в россии компания ЭФО // http://altera.ru

2015-05-10

2015-05-10 1022

1022