21. Сумматор. Функциональная схема одноразрядного сумматора.

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов. В зависимости от формы представления информации различают сумматоры аналоговые и цифровые.

Узел ЭВМ выполняющий арифметическое суммирование кодов чисел, называется сумматором. Операция суммирования осуществляется в сумматорах поразрядно с использованием одноразрядных суммирующих схем. При этом в каждом разряде требуется выполнить сложение трех двоичных цифр данного разряда первого слагаемого Хi цифры этого же разряда второго слагаемого Yi и цифры переноса Pi из соседнего младшего разряда.

И тогда такое суммирование разбивают на две аналогичные операции: суммирование двух цифр слагаемых и суммирование полученного результата с переносом из соседнего младшего разряда. Каждая из этих операций выполняется схемой, называемой полусумматором.

| Х I | Y i | S i | P i+1 |

В таблице приведена логика работы сумматора на два входа X i и Yi. На его выходах образуется сумма Si данного разряда и осуществляется перенос Рi+1 в следующий старший разряд. По таблице можно составить логическое выражение для суммы Si и переноса Р i+1:

Преобразуем выражение для суммы к виду:

На рисунке 11.1 приведены функциональная схема полусумматора, составленная в соответствии с полученными логическими выражениями, и условное обозначение его. Схема является комбинационной и реализуется на логических элементах.

Логика работы одноразрядного сумматора на три входа или полного сумматора приведена в таблице А, где Xi, Yi - суммируемые двоичные цифры в i-м разряде, Pi - перенос из младшего разряда, Si - образующаяся сумма данного разряда и осуществляет перенос Pi+1 в следующий старший разряд.

Таблица А.

| Xi | Yi | Pi | SI | Pi+1 |

По таблице можно составить логические выражения:

По этим выражениям также можно составить функциональную схему комбинационного сумматора с использованием соответствующих логических элементов. Однако, вначале целесообразно эти выражения преобразовать так, чтобы в формулах для Si и Pi+1 были по возможности одинаковые члены, что, естественно, сократит количество используемых элементов. Один из вариантов таких преобразований дают выражения:

которым соответствуют функциональная схема и условное обозначение сумматора, приведенные на рис.11.2.

Комбинационный сумматор можно реализовать также с использованием двух полусумматоров и логического элемента ИЛИ, как показано на рис.11.3.

В реальных электронных схемах сумматор изображается так.

рис.11.5.

Эта схема называется одноразрядным сумматором.

| Число 1 | Число 2 | Ст.разряд | Мл.разряд |

| Вх.1 | Вх.2 | Вых.1 | Вых.2 |

22. Триггер. Основные характеристики.

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

| Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю. |

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает "хлопанье". Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить ("перебрасываться") из одного электрического состояния в другое и наоборот.

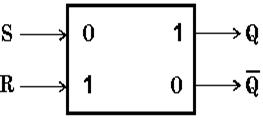

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис. 5.6.

Рис. 5.6

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал Q является логическим отрицанием сигнала

, причем выходной сигнал Q является логическим отрицанием сигнала  .

.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов ( ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

Рис. 5.7

| S | R | Q |  |

| запрещено | |||

| хранение бита |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ (табл. 5.5).

1. Если на входы триггера подать S="1", R="0", то (независимо от состояния) на выходе Q верхнего вентиля появится "0". После этого на входах нижнего вентиля окажется R="0", Q="0" и выход  станет равным "1".

станет равным "1".

2. Точно так же при подаче "0" на вход S и "1" на вход R на выходе  появится "0", а на Q — "1".

появится "0", а на Q — "1".

3. Если на входы R и S подана логическая "1", то состояние Q и  не меняется.

не меняется.

4. Подача на оба входа R и S логического "0" может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

2015-05-30

2015-05-30 1192

1192