Большинство стандартных устройств, работающих с однопроводной шиной DALLAS, представляют собой пассивное устройство (без внутреннего источника питания). К таким устройствам относятся, в частности, датчики температуры DS18B20 и электронные ключи DS1990A.

Для упрощения дальнейшего описания условно назовем такие устройства DS.

DS всегда является подчинённым устройством, а мастером является обычно микропроцессор.

Последовательность доступа к DS по 1-проводной шине следующая:

– инициализация,

– команда чтения кода сигнатуры,

– чтение данных.

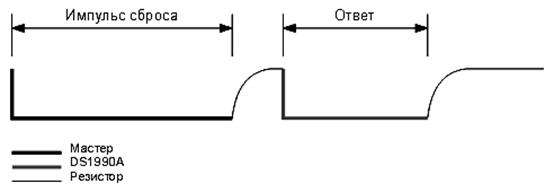

Все пересылки по 1-проводной шине начинаются с инициализации. Инициализация производится в последовательности, показанной на рис. 9.5.

Рис. 9.5. Инициализация обмена по 1-проводной шине

Инициализация выполняется в следующей последовательности:

– мастер посылает импульс сброса (reset pulse) – сигнал низкого уровня длительностью не менее 480 мкс;

– за импульсом сброса следует ответ подчиненного устройства (presence

pulse) – сигнал низкого уровня длительностью 60-240 мкс, который генерируется через 15-60 мкс после завершения импульса сброса.

Ответ подчиненного устройства даёт мастеру понять, что на шине присутствует устройство DS и оно готово к обмену. После того как мастер обнаружил ответ, он может передавать команду чтения устройства DS. Команда чтения имеет код 33H.

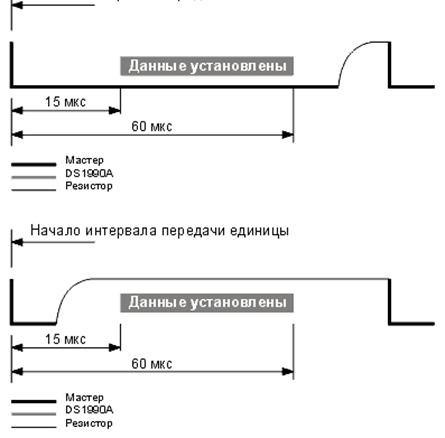

Передача данных ведётся путём формирования специальных временных интервалов (time slots). Каждый временной интервал служит для передачи одного бита. Первым передаётся младший бит. Интервал начинается импульсом низкого уровня, длительность которого лежит в пределах 1-15 мкс.

Поскольку переход из "1" в "0" менее чувствителен к ёмкости шины (он формируется открытым транзистором, в то время как переход из нуля в единицу формируется подтягивающим резистором), именно этот переход DS использует для синхронизации с мастером.

В DS запускается схема временной задержки, которая определяет момент считывания данных. Номинальное значение задержки равно 30 мкс, однако оно может колебаться в пределах 15 – 60 мкс. За импульсом низкого уровня следует передаваемый бит. Он должен удерживаться на шине 60 – 120 мкс от начала интервала.

Временной интервал завершается переводом шины в "1" на время не менее 1 мкс. Это необходимо для зарядки внутреннего конденсатора, который обеспечивает питание DS. Аналогичным образом формируются временные интервалы для всех передаваемых битов (рис 9.6).

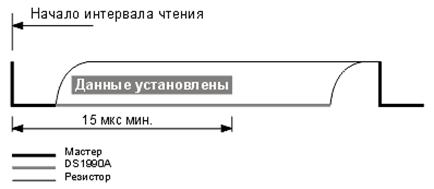

Приняв команду чтения, DS передает 8-битный код типа устройства (например, для DS18В20 это 28h), 48-битный серийный номер и 8-битную контрольную сумму. Временные интервалы для принимаемых битов тоже формирует мастер.

Интервал начинается импульсом низкого уровня длительностью 1 – 15 мкс. Затем мастер должен освободить шину, чтобы дать возможность DS вывести бит данных. По переходу из единицы в нуль DS выводит на шину бит данных и запускает схему временной задержки, которая определяет, как долго бит данных будет присутствовать на шине. Это время лежит в пределах 15 – 60 мкс. Для того чтобы данные на шине гарантированно установились, требуется некоторое время. Поэтому момент считывания данных мастером должен отстоять чуть меньше чем на 15 мкс от начала временного интервала (рис. 9.7).

|

Рис. 9.6. Интервалы записи нуля и единицы по 1-проводной шине

Рис. 9.7. Интервал чтения по 1-проводной шине

Правильность принятых данных проверяется с помощью контрольной суммы. Если подсчитать контрольную сумму всех восьми считанных байтов (включая байт считанной контрольной суммы), то в случае отсутствия ошибок должен получиться нуль. Для определения контрольной суммы в DS используется специальная подпрограмма. Эта подпрограмма должна вызываться для каждого байта, участвующего в подсчете контрольной суммы. Байт должен быть помещён в регистр. Контрольная сумма получается в некоторой ячейке памяти (перед началом подсчёта контрольной суммы эта ячейка должна быть обнулена).

9.4. Применение двухпроводной шины I2C

Конфигурация системы на примере МК DS5000 показана на рис. 9.8. DS1307 имеет двухпроводную шину, подключённую к двум выводам порта I/O DS5000: SCL и SDA. Напряжение VDD равно 5 В, RP = 5 кОм. DS5000 использует кварцевый резонатор с частотой 12 МГц. Периферийными устройствами могут быть любые устройства, поддерживающие протокол двухпроводного интерфейса, например цифровой термометр и термостат DS1621. Подключение к DS5000 осуществлялось с использованием аппаратного и программного обеспечения макета DS5000T. Этот макет позволяет применять ПК в качестве терминала ввода/вывода, используя последовательные порты DS5000 для соединения с клавиатурой и монитором.

Рис. 9.8. Типовая конфигурация двухпроводной шины

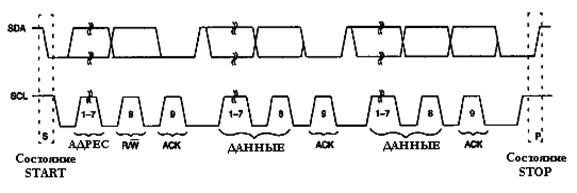

В процессе передачи данных, при переходе линии тактового сигнала в высокое состояние, линия данных должна оставаться стабильной. Изменения состояния линии данных в тот момент, когда тактовая линия находится в высоком состоянии, будут пониматься как управляющие сигналы.

В соответствии с этим должны быть оговорены следующие условия.

1. Начало передачи данных. Изменение состояния линии данных при переходе из высокого в низкое, в то время как тактовая линия находится в высоком состоянии, определяется как состояние START.

2. Остановка передачи данных. Изменение состояния линии данных при переходе из низкого в высокое, в то время как тактовая линия находится в высоком состоянии, определяется как состояние STOP.

3. Действительные данные. Состояние линии данных соответствует действительным данным тогда, когда после условия START линия данных стабильна во время высокого состояния тактового сигнала. Данные на линии должны быть изменены во время низкого состояния тактового сигнала. Один тактовый импульс на один бит данных.

4. Каждая передача данных начинается при наступлении состояния START и прекращается при наступлении состояния STOP. Количество байт данных, переданных между состояниями START и STOP, не ограничено и определяется "ведущим" устройством. Информация передаётся побайтно, и каждый приём подтверждается девятым битом.

5. Подтверждение приёма. Каждое приёмное устройство, при обращении к нему, вынуждено генерировать подтверждение приёма после получения каждого байта. "Ведущее" устройство должно генерировать дополнительные тактовые импульсы, которые ставятся в соответствие битам подтверждения.

Если сигнал подтверждения приёма находится в высоком состоянии, то по приходу тактового импульса бита подтверждения подтверждающее приём устройство должно переводить линию SDA в низкое состояние. Конечно, должны учитываться время установки и время удержания. "Ведущее" устройство должно сигнализировать об окончании передачи данных "ведомому" устройству, прекращая генерацию бита подтверждения, при получении от "ведомого" тактового импульса подтверждения приёма. В этом случае "ведомый" должен перевести линию данных в низкое состояние, чтобы позволить "ведущему" генерировать условие STOP.

На рис. 9.9 показано завершение передачи данных по двухпроводной линии. В зависимости от состояния бита R/#W возможны два типа передачи.

1. Данные передаются от "ведущего" передатчика "ведомому" приёмнику. Первый байт, передаваемый "ведущим", является адресом "ведомого". Затем следует последовательность байтов данных. "Ведомый" возвращает биты подтверждения приёма после каждого принятого байта. Порядок передачи данных: первым является самый старший разряд (MSB).

2. Данные передаются от "ведомого" передатчика "ведущему" приёмнику. Первый байт (адрес "ведомого") передаётся "ведущему". Затем "ведущий" возвращает бит подтверждения. Это следует за передачей "ведомым" последовательности данных. "Ведущий" возвращает бит подтверждения приёма после каждого принятого байта, за исключением последнего байта. После принятия последнего байта бит подтверждения приёма не возвращается.

Рис. 9.9. Передача данных по последовательной двухпроводной шине

"Ведущее" устройство генерирует все тактовые импульсы и состояния START и STOP. Передача заканчивается при возникновении состояния STOP или повторного возникновения состояния START. Так как повторное состояние START является началом следующей последовательной передачи, то шина не освобождается. Порядок передачи данных: первым является самый старший разряд (MSB).

Устройство I2C может работать в двух режимах.

1.Режим "ведомого" приемника (режим записи DS1307). Последовательные данные и такты получены через SDA и SCL соответственно. После передачи каждого байта передаётся подтверждающий бит. Состояния START и STOP понимаются как начало и конец последовательной передачи. Распознавание адреса выполняется аппаратно после приема адреса "ведомого" и бита направления (рис. 9.10). Байт адреса является первым байтом, принимаемым после возникновения состояния START, генерируемого "ведущим". Байт адреса содержит семь битов адреса, сопровождаемых битом направления (R/#W), который для записи равен "0". После приёма и декодирования байта адреса "ведомый" выдаёт подтверждение на линию SDA. После подтверждения адреса "ведомого" и бита записи "ведущий" передает адрес регистра "ведомого", к которому производится обращение. Тем самым будет установлен указатель регистра в "ведомом". Затем "ведущий" начнет передавать каждый байт данных с последующим приёмом подтверждения получения каждого байта. По окончании записи "ведущий" сформирует состояние STOP для прекращения передачи данных.

Адрес ведомого R/W Адрес слова Данные (n) Данные (n+1) Данные (n+Х)

| S | A | XXXXXXXX | A | XXXXXXXX | A | XXXXXXXX | A | XXXXXXXX | NA | P |

ПРИЕМ ДАННЫХ(Х + 1 байтов)

S – старт

А – подтверждение приема

Р – стоп

Рис. 9.10. Запись данных – режим "ведомого" приёмника

2.Режим "ведомого" передатчика (режим чтения из ведомого). Первый байт принимается и обрабатывается как в режиме "ведомого" приёмника. Однако в этом режиме бит направления укажет, что направление передачи изменено. Последовательные данные передаются "ведомым" по SDA, тактовые импульсы – по SCL. Состояния START и STOP понимаются как начало и конец последовательной передачи (рис. 9.11).

Адрес ведомого R/W Адрес слова Данные (n) Данные (n+1) Данные (n+Х)

| S | A | XXXXXXXX | A | XXXXXXXX | A | XXXXXXXX | A | XXXXXXXX | NA | P |

ПЕРЕДАЧА ДАННЫХ(Х + 1 байтов)

S – старт

А – подтверждение приема

Р – стоп

NA – неподтверждение приема

Рис. 9.11. Чтение данных – режим "ведомого" передатчика

Примечание. За последним байтом данных следует неподтверждение.

Байт адреса является первым байтом, принимаемым после возникновения состояния START, генерируемого "ведущим". Байт адреса содержит семь битов адреса "ведущего", сопровождаемых битом направления (R/#W), который для чтения равен "1". После приёма и декодирования байта адреса "ведомый" принимает подтверждение с линии SDA. Тогда "ведомый" начинает передавать данные с адреса, на который показывает указатель регистра. Если указатель регистра не записан перед инициализацией режима чтения, то первым прочитанным адресом является последним адрес, сохранённый в указателе регистра. "Ведомый" должен послать бит "неподтверждения", чтобы закончить чтение.

Контрольные вопросы

1. Как выполняется подтверждение приёма данных в шине I2C?

2. Какой сигнал является сигналом квитирования "разрешено начало/завершение цикла обмена" при работе LPT порта в режиме ЕРР?

3. Для чего служит сигнал ReverseRequest# = 0 при работе LPT порта в режиме ЕСР?

4. Какой из режимов работы LPT порта позволяет обеспечить максимальную скорость обмена данными между ЭВМ и периферийным устройством?

5. Сколько линий достаточно для обмена данными между ЭВМ и микроконтроллером посредством интерфейса RS232 при использовании режима с частичным квитированием (общий провод не учитывать)?

6. Укажите правильную последовательность доступа к однопроводной шине DALLAS.

7. Укажите правильную последовательность инициализации при работе с однопроводной шиной DALLAS.

8. Как формируется сигнал START при использовании шины I2C?

9. Как формируется сигнал STOP при использовании шины I2C?

10. Какие задачи совместимости и сопряжения модулей прибора или системы решает интерфейс?

11. Какой из режимов работы интерфейса RS232 может использоваться в режиме работы по прерыванию?

10. ЭЛЕМЕНТЫ МИКРОПРОЦЕССОРНОЙ

ТЕХНИКИ В ЦИУ

В настоящее время широкое распространение в электронных устройствах самого различного назначения нашли микроконтроллеры (МК). Микроконтроллеры объединяют все передовые технологии микропроцессорной техники: использование электрически однократно и многократно программируемого пользователем ППЗУ, минимальное энергопотребление, исключительную производительность, RISC и CISC архитектуру и минимальные размеры корпуса. Эти широкие возможности и низкая стоимость сделали МК лучшим выбором для инженерных применений. Использовать микроконтроллеры рекомендуется во всех случаях, когда критично энергопотребление, габариты и стоимость устройства.

Мировыми лидерами в производстве микроконтроллеров являются корпорации: Microchip, выпускающая МК семейства PIC, и Atmel, выпускающая МК семейства AVR и MCS-51. Семейство MCS-51, реализующее архитектуру процессора XA, стало, по сути дела, прародителем семейств PIC и AVR микроконтроллеров, выполненных по гарвардской архитектуре процессора.

В гарвардской архитектуре разделена память программ и память данных. Обращение к памяти происходит по отдельным шинам адреса и данных, что значительно повышает производительность процессора по сравнению с традиционной архитектурой.

В микроконтроллерах с традиционной архитектурой ядра команды и данные запрашиваются по одной и той же шине. Чтобы выполнить выборку команды, необходимо сделать несколько запросов по 8-разрядной (или кратной 8 разрядам) шине. Затем (если необходимо) запросить данные, выполнить команду и сохранить результат. Как может быть замечено, шина с традиционной архитектурой ядра значительно загружена.

В последние годы, ввиду высоких требований к быстродействию МК при условии их низкой стоимости и энергопотребления, разработки на основе MCS-51 МК выполняются несколько реже по сравнению с разработками на PIC и AVR микроконтроллерах. Поэтому в данной главе пособия будут рассмотрены основные особенности и применение именно PIC и AVR МК.

10.1. Общие сведения о микроконтроллерах

семейства PICmicro

Микроконтроллеры PICmicro построены по RISC архитектуре. Это предполагает, что все инструкции имеют одну длину и выбираются за один машинный цикл. Набор инструкций этих микроконтроллеров широкий, тщательно подобранный специально для задач управления. Гарвардская архитектура процессора, широкое слово инструкции, очередь команд, RISC набор команд – все это позволило добиться высокого быстродействия и получить компактный код. Все команды микроконтроллера, за исключением команд перехода, выполняются за один машинный цикл, составляющий 4 периода тактового генератора.

Все микроконтроллеры PICmicro имеют расположенную на кристалле кодовую память. Большинство микроконтроллеров снабжено дешевой однократно программируемой (OTP) памятью. Наряду с OTP кодовой памятью Microchip выпускает и микроконтроллеры с масочной памятью, а также перепрограммируемой памятью с ультрафиолетовым стиранием и FLASH памятью.

Микроконтроллеры PICmicro работают в очень широком диапазоне частот внешнего тактового генератора (до 33 МГц) и имеют несколько режимов встроенного тактового генератора, позволяющего работать на частотах от 32 кГц до 33 МГц.

Микроконтроллеры не требуют традиционных внешних цепей для формирования сигнала сброса. Они вырабатывают его автоматически при включении питания или при подаче внешнего сигнала сброса.

Микроконтроллеры PICmicro работают в очень широком диапазоне питающих напряжений, у некоторых образцов питание может изменяться в пределах 2–6 В. Микроконтроллеры характеризуются и очень низкими токами потребления. В режиме пониженного энергопотребления ток потребления снижается до десятых долей микроампер.

Семейство PICmicro подразделяется на четыре подсемейства:

1) PIC16C5x – базовое семейство с 12-битной архитектурой;

2) PIC16Cxx – среднее семейство с 14-битной архитектурой;

3) PIC17Cxx, PIC18Cxx – старшее семейство с 16-битной архитектурой;

4) PIC12Cxx – семейство в 8-выводных корпусах с 12/14-битной архитектурой.

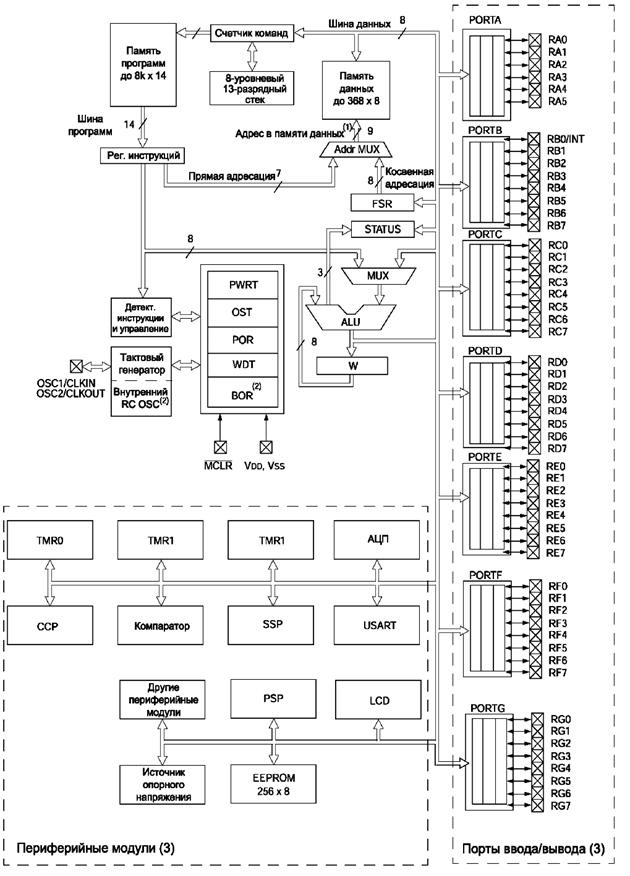

Обобщенная структурная схема PIC МК приведена на рис. 10.1.

|

|

Каждая часть микроконтроллера может быть отнесена к одной из трех групп:

1) ядро микроконтроллера;

2) периферийные модули;

3) специальные особенности микроконтроллеров.

2017-11-30

2017-11-30 1215

1215