Регистр. Временная диаграмма.

Для хранения информации в виде многоразрядных двоичных чисел (двоичного кода) служит регистр. В отличие от постоянных запоминающих устройств долговременной памяти в регистрах осуществляется кратковременное запоминание (регистрация)информации на период одного или нескольких циклов работы всей системы. Запоминающими элементами регистра, количество которых равно количеству разрядов двоичного числа, служат триггеры. Обычно регистры выполняют на основе RS-,D-, JK-триггеров. Для выполнения вспомогательных операций: ввода в регистр или вывода из него хранимого числа, преобразования кода двоичного числа, сдвига числа на определенное число разрядов влево или вправо применяют комбинированные схемы на основе логических элементов.

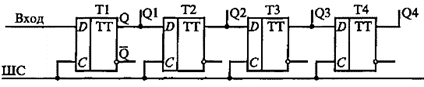

Регистр сдвига предназначен для хранения и поразрядного сдвига (вправо, влево) хранящихся в нем чисел путем подачи импульсов на шину сдвига ШС. На рис. 2.62, а приведен регистр сдвига, выполненный на D-

триггерах. Количество триггеров в регистре соответствует числу разрядов. Каждый триггер служит для хранения кода одного разряда запоминаемого двоичного числа.

В рассматриваемом случае регистр предназначен для хранения четырехразрядного двоичного числа. Выход Q каждого предыдущего триггера объединяют с входом D последующего

Информация в виде последовательного кода поступает на выход L

первого триггера, начиная с низшего разряда кода. кода. Синхронизирующие входы С триггеров, подключенные к шинке сдвига ШС, используются для перемещения записанного числового кода вправо. Представим, что в регистр сдвига необходимо

записать число 1011. На вход триггера Т1 поступает сигнал 1, соответствующий единице низшего разряда. В триггере Т1 записывается 1. На вход С триггеров поступает тактовый импульс с шинки

сдвига, который перемещает 1 в триггер Т2. В триггер Т1 поступает на вход D сигнал 1 второго разряда числа и записывается в нем. После очередного тактового импульса на шинке сдвига единицы переходят с Т2 в ТЗ, а с Т1 в Т2. На вход D триггера Т1 поступает и записывается в нем сигнал 0. Следующий тактовый импульс перемещает единицы из Т2 и ТЗ в ТЗ и Т4, а нуль — в Т2. На вход Т1

поступает единица четвертого разряда, таким образом, число полностью вводится в регистр после тактового импульса: на выходах Ql, Q2, Q3, Q4 присутствует сигнал 1011. Как видно из описания, при каждом тактовом импульсе двоичная комбинация, включая

сигнал на входе регистра, перемещается вправо. Если переключить связи между разрядами так, чтобы выход Q каждого высшего разряда связать со входом D-триггера ближайшего низшего разряда, то при поступлении тактового импульса число

будет перемещаться влево.

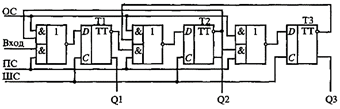

Направление сдвига можно менять сигналами, подаваемыми на

шинки прямого (ПС) и обратного (ОС) сдвигов, которые подключаются с помощью схем И-НЕ к триггерам.

Выход Q каждого триггера (кроме первого) связан со схемой И на входе предыдущего для обеспечения обратного сдвига кодовой комбинации при

подаче тактовых импульсов на шинку ОС. Таким образом, представленный на рис. регистр сдвига является реверсивным трехразрядным. Информация, записанная в регистре в виде двоичного числа, выводится из него через выходы триггеров Ql, Q2, Q3.Регистры сдвига используются для выполнения математических и логических операций над числовыми кодовыми комбинациями.

Сумматоры - это цифровые функциональные устройства, предназначенные для выполнения операции сложения чисел, представленных в различных кодах.

По характеру действия сумматоры подразделяются на комбинационные, не имеющие элементов памяти, и накапливающие – запоминающие результаты вычислений при снятии входных сигналов.

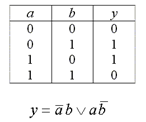

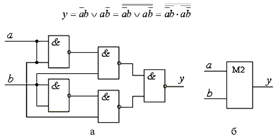

В дальнейшем будут рассматриваться только комбинационные сумматоры, на основе которых выполняется большинство суммирующих ИС. Сумматор по модулю два - Это устройство с двумя входами (а и b), на выходе у которого сигнал "1" появляется только в том случае, когда на входах действуют противоположные сигналы, т. е. "0" и "1". Сумматор не обладает памятью. Его таблица истинности и логическое уравнение имеют вид:

Название “по модулю два” этот сумматор получил потому, что y соответствует значению младшего разряда при суммировании одноразрядных двоичных чисел A и B. Построим в базисе И–НЕ схему сумматора по модулю два (рис. 21)

Название “по модулю два” этот сумматор получил потому, что y соответствует значению младшего разряда при суммировании одноразрядных двоичных чисел A и B. Построим в базисе И–НЕ схему сумматора по модулю два (рис. 21)

а – принципиальная схема; б – функциональная схема

2014-02-24

2014-02-24 5377

5377