3-1. Схема задержки на основе интегрирующей цепи.

Наряду с формирователями и генераторами сигналов на базе операционных усилителей, рассмотренных ранее, широко используются схемы на базе логических элементов. Электрические параметры входных и выходных сигналов таких схем определяются типами используемых в них интегральных логических элементов и, поэтому, эти схемы широко используются в качестве времязадающих, генерирующих и синхронизирующих узлов цифровой электроники. Рассмотрим схемотехнику и принципы работы некоторых таких схем.

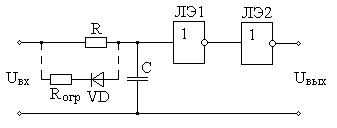

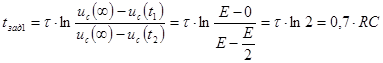

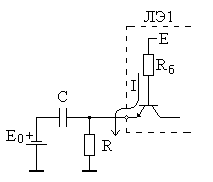

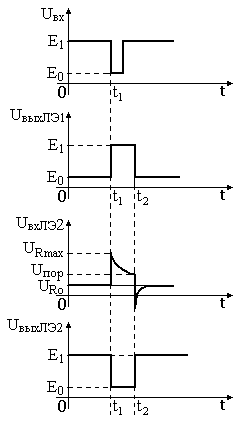

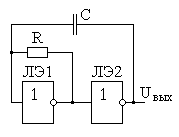

Схема задержки на основе интегрирующей RC-цепи и логических элементов (инверторов) представлена на рис. 3.1.

Рис. 3.1. Схема задержки на основе интегрирующей цепи и логических элементов.

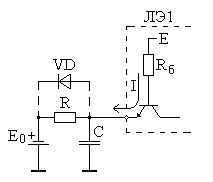

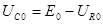

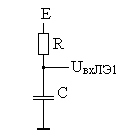

Будем считать, что в схеме используются элементы ТТЛ-типа, напряжение на вход всей схемы поступает с выхода аналогичного элемента ТТЛ-типа и последовательная цепь из диода VD и резистора Rогр в схему не включена. В исходном состоянии на входе схемы действует напряжение логического нуля E 0. Для элементов ТТЛ-типа E 0=0,2 В, E 1=3,5 В, Uпор =1,5 В. Для определения напряжения на конденсаторе в исходном состоянии рассмотрим входную цепь логического элемента (рис. 3.2):

Рис. 3.2. Входная интегрирующая цепь с логическим элементом ТТЛ.

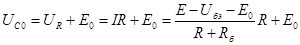

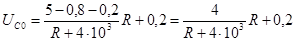

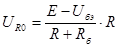

Для этой цепи можно записать

,

,

где для элементов ТТЛ-типа E =5 B; Uбэ =0,8 В; Rб =4 кОм.

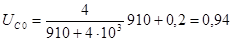

Таким образом, имеем

.

.

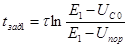

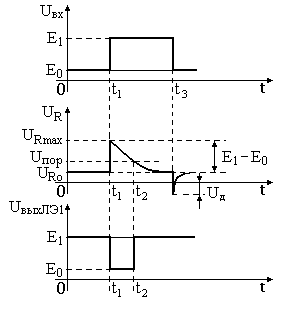

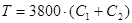

В момент времени t 1 напряжение Uвх становится равным уровню логической единицы E 1. Конденсатор начинает заряжаться через резистор R и в момент времени t 2 напряжение на конденсаторе достигнет значения Uпор, при котором срабатывает логический элемент ЛЭ1, а значит и ЛЭ2 (рис. 3.3).

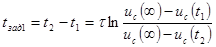

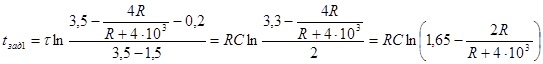

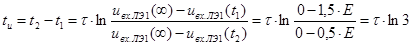

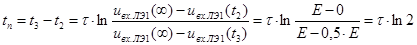

Для величины задержки переднего фронта входного импульса имеем

.

.

После подстановки установившихся значений uc (t) получим

.

.

Рис. 3.3. Временная диаграмма работы схемы задержки на основе интегрирующей цепи.

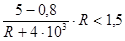

Поскольку заряд конденсатора осуществляется через резистор R, то  . Очевидно, что для формирования задержки отличной от нуля должно выполняться условие UС 0< Uпор, т.е.

. Очевидно, что для формирования задержки отличной от нуля должно выполняться условие UС 0< Uпор, т.е.

.

.

Решая неравенство, получаем R <1,9 кОм.

Подставим значения:

.

.

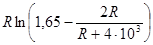

Из полученной формулы следует, что с увеличением R задержка возрастает за счет увеличения t, а с другой стороны, уменьшается за счет уменьшения значения логарифма. Наибольшего значения выражение  достигает при R =930 Ом. Выбираем ближайший к полученному значению номинал из стандартного ряда R =910 Ом. В этом случае получаем

достигает при R =930 Ом. Выбираем ближайший к полученному значению номинал из стандартного ряда R =910 Ом. В этом случае получаем

или

или

.

.

С окончанием входного импульса конденсатор разряжается через резистор R и переход коллектор-эмиттер предыдущего логического элемента. При этом

.

.

При R =910 Ом имеем

В;

В;

.

.

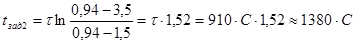

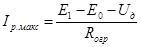

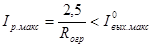

На практике часто требуется получить задержку только переднего фронта. При этом задержка заднего фронта не имеет значения. В этом случае необходимо, чтобы схема возвращалась в исходное состояние сразу с окончанием импульса на входе т.е. следует сократить время разряда конденсатора C. Для этого параллельно резистору R включается последовательная цепочка из диода VD и ограничительного резистора Rогр. Разряд конденсатора в этом случае происходит через диод, ограничительный резистор и переход коллектор–эмиттер предыдущего логического элемента. Резистор Rогр необходим для того, чтобы ток разряда конденсатора не превышал значения  максимального выходного тока логического нуля используемого логического элемента в предыдущем каскаде, например, 16 мА для элемента 155 серии или 8 мА для элемента 555 серии. Максимальное значение тока разряда для схемы рис. 3.1 равно

максимального выходного тока логического нуля используемого логического элемента в предыдущем каскаде, например, 16 мА для элемента 155 серии или 8 мА для элемента 555 серии. Максимальное значение тока разряда для схемы рис. 3.1 равно

.

.

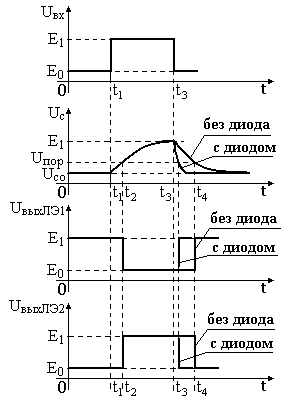

Таким образом, должно выполняться условие:  .

.

Учитывая, что для кремниевых диодов прямое падение напряжения  В, то после подстановки получим условие для определения

В, то после подстановки получим условие для определения

или

или

.

.

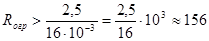

Так для элементов 155 серии

Ом.

Ом.

Ближайший номинал из стандартного ряда равен 160 Ом.

Использование Rогр позволяет также сохранять на выходе предыдущего логического элемента уровень логического нуля при разряде конденсатора, что может быть важным, если этот выход подсоединен еще к каким–либо элементам. Таким образом, получаем

.

.

В большинстве практических случаев резистор Rогр не ставится. При этом ток разряда может превысить допустимое значение I 0вых, что приведет к увеличению напряжения на выходе предыдущего элемента. Однако, поскольку разряд конденсатора происходит очень быстро, то ток разряда не приводит к тепловому пробою выходного транзистора предыдущего логического элемента.

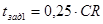

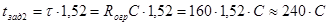

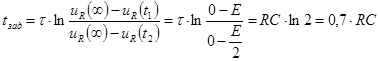

В случае использования элементов КМОП-типа можно принять:  ,

,  и

и  . Таким образом, для задержки переднего фронта получим

. Таким образом, для задержки переднего фронта получим

.

.

При этом tзад2 определяется той же формулой т.е.  .

.

При использовании элементов КМОП-типа особое внимание следует обращать на величину токов заряда и разряда конденсатора, которые протекают через выходные транзисторы предыдущего логического элемента и не должны превышать значения  мА.

мА.

3-2. Схема задержки на основе дифференцирующей цепи.

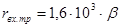

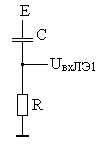

Схема задержки на основе дифференцирующей RC -цепи и логического элемента представлена на рис. 3.4. Как и в предыдущей схеме, считаем, что рассматриваемый логический элемент ЛЭ1 ТТЛ-типа.

Рис. 3.4. Схема задержки на основе дифференцирующей цепи и логического элемента.

В исходном состоянии на входе схемы присутствует уровень напряжения логического нуля. В соответствии с рис. 3.5 на входе ЛЭ1, т.е. на резисторе R действует напряжение UR 0, равное

.

.

Рис. 3.5. Входная дифференцирующая цепь с логическим элементом.

Очевидно, должно выполняться UR 0< Uпор , откуда

,

,

т.е. R<2,2 кОм. Практически выбирают Rmax =1,6 кОм.

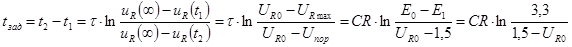

Напряжение на конденсаторе в исходном состоянии  . В момент t 1 на вход подается положительный перепад напряжения, равный (E 1- E 0) (рис. 3.6).

. В момент t 1 на вход подается положительный перепад напряжения, равный (E 1- E 0) (рис. 3.6).

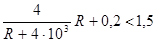

Рис. 3.6. Временная диаграмма работы схемы задержки на основе дифференцирующей цепи.

По закону коммутации весь перепад выделяется на резисторе R, т.е. напряжение на R увеличивается на (E1-E0) и становится равным

.

.

По мере заряда конденсатора напряжение на R стремится к исходному уровню UR 0.Пока это напряжение остается большим Uпор, на выходе ЛЭ1 будет логический нуль. Задержка положительного фронта равна

Проанализируем выражение  , полученное после подстановки выражения для

, полученное после подстановки выражения для  и выполнения ряда преобразований. Очевидно, что tзад увеличивается с увеличением R. При

и выполнения ряда преобразований. Очевидно, что tзад увеличивается с увеличением R. При  , получаем

, получаем

В;

В;

.

.

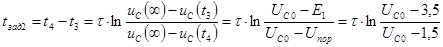

В момент t 3 окончания входного импульса, когда на вход всей схемы подается уровень логического нуля, по закону коммутации на вход ЛЭ1 поступает отрицательный перепад напряжения, поскольку конденсатор оказывается подключенным в обратной полярности. При этом происходит быстрый разряд конденсатора через защитный диод, стоящий на входе логического элемента.

В случае использования элементов КМОП-типа, для которых  ,

,  и

и  , имеем

, имеем

.

.

3-3. Одновибраторы и мультивибраторы.

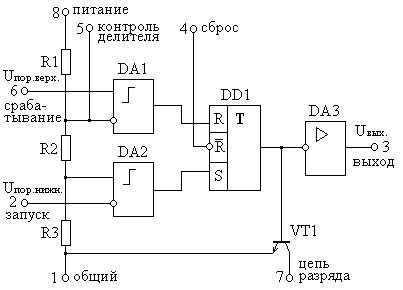

Наряду со схемами задержки широко используются схемы генераторов одиночных импульсов и последовательностей импульсов. К генераторам одиночных импульсов относится ждущий мультивибратор или одновибратор. Ждущий мультивибратор (одновибратор) – это устройство с одним устойчивым и одним неустойчивым состоянием, длительность которого определяется внутренними переходными процессами времязадающих реактивных цепей. После пребывания в неустойчивом состоянии ждущий мультивибратор снова возвращается в устойчивое состояние. Для перевода одновибратора в неустойчивое состояние на его вход подается запускающий импульс. Таким образом, при подаче на вход короткого запускающего импульса, одновибратор вырабатывает на выходе импульс фиксированной длительности.

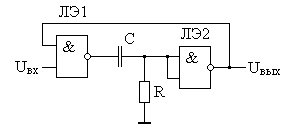

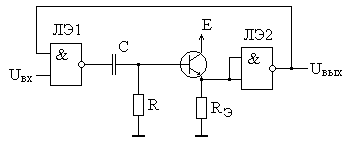

Схема ждущего мультивибратора на двух логических элементах и RC-цепи представлена на рис. 3.7.

Рис. 3.7. Схема ждущего мультивибратора.

В состав ждущего мультивибратора входят логические элементы ЛЭ1, ЛЭ2 и RC-цепь. При этом, ЛЭ2 и RC-цепь образуют схему задержки на основе дифференцирующей цепи, рассмотренную выше. Источником входного импульса для нее является выход элемента ЛЭ1. Схема задержки формирует задержку входного импульса на величину tзад. В устойчивом состоянии, поскольку на входе ЛЭ2 действует напряжение UR0, меньшее Uпор, на выходе схемы присутствует логическая единица, которая одновременно подается на один из входов ЛЭ1. Если при этом на другой вход ЛЭ1 (Uвх) также подавать логическую единицу, то на выходе ЛЭ1 сохраняется логический нуль. Схема, таким образом, находится в устойчивом состоянии (рис. 3.8). Подав теперь на вход Uвх напряжение логического нуля, на выходе ЛЭ1 сформируется напряжение логической единицы, которое через конденсатор передастся на ЛЭ2. На входе ЛЭ2 напряжение возрастет до значения UR max и на его выходе сформируется логический нуль. По мере заряда конденсатора, напряжение на входе ЛЭ2 будет стремиться к значению UR0. В момент равенства напряжения на входе ЛЭ2 значению Uпор, на выходе ЛЭ сформируется логическая единица и схема вернется в устойчивое состояние. Длительность выходного импульса будет определяться длительностью задержки tзад, задаваемой схемой задержки на элементе ЛЭ2, конденсаторе и резисторе.

Рис. 3.8. Временная диаграмма работы ждущего мультивибратора.

Выше было показано, что R должно удовлетворять условию R <2,2 кОм, на практике Rмакс =1,6 кОм. Для увеличения tзад можно увеличивать только емкость, что приводит к увеличению габаритов устройства. Чтобы увеличить tзад за счет увеличения сопротивления зарядной цепи используют схему с эмиттерным повторителем, которая приведена на рис. 3.9.

Рис. 3.9. Схема ждущего мультивибратора с эмиттерным повторителем.

Имеем  кОм. Входное сопротивление транзисторной цепи определяется как

кОм. Входное сопротивление транзисторной цепи определяется как

.

.

Типовое расчетное значение для  выбираем 100. Таким образом,

выбираем 100. Таким образом,

кОм.

кОм.

Выбираем  , т.е. выбираем из стандартного ряда

, т.е. выбираем из стандартного ряда  , тогда эквивалентное сопротивление выражается как сопротивление параллельной цепи из R и rвх.тр

, тогда эквивалентное сопротивление выражается как сопротивление параллельной цепи из R и rвх.тр

кОм.

кОм.

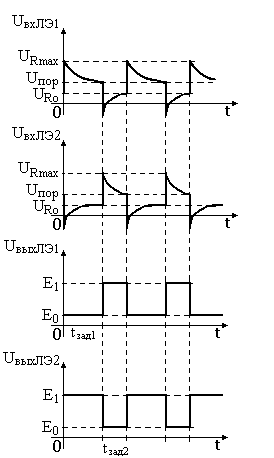

Таким образом, если без эмиттерного повторителя tзад =3800× С, то в данном случае

,

,

т.е. tзад увеличилась почти в 20 раз.

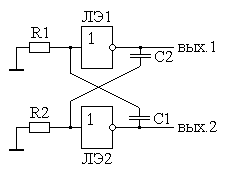

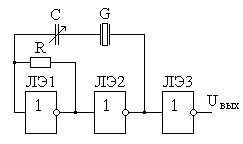

Если входы двух схем задержек на основе дифференцирующей RC-цепи и логического элемента замкнуть с выходами друг друга, то получится схема автоколебательного мультивибратора или просто мультивибратора (рис. 3.10), задача которого генерировать последовательность прямоугольных импульсов. В данной схеме можно выделить две схемы задержки: первая - на элементах ЛЭ1, R 1 и C 1, вторая - на элементах ЛЭ2, R 2 и C 2. Такая схема относится к классу релаксационных генераторов.

Рис. 3.10. Схема мультивибратора на двух логических элементах и дифференцирующих цепях.

Особенностью мультивибратора является то, что, хотя каждая из образующих его схем задержек имеет устойчивое состояние, целиком вся схема устойчивого состояния не имеет. Таким образом, логическая единица с выхода одного элемента (ЛЭ1) перебрасывает другой элемент (ЛЭ2) в противоположное состояние. Тот, в свою очередь, меняет на противоположное состояние первого элемента (ЛЭ1) и т.д., т.е. возникает колебательный процесс, незатухающий за счет наличия источника питания и активных элементов ЛЭ1 и ЛЭ2. Для элементов ТТЛ-типа временная диаграмма работы представлена на рис. 3.11. Длительности импульса и паузы, составляющие период колебаний, определяются величинами задержек первой и второй схем tзад1 и tзад2:

или при R 1= R 2=1,6 кОм

.

.

Рис. 3.11. Временная диаграмма работы мультивибратора на двух логических элементах и дифференцирующих цепях.

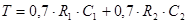

Для элементов КМОП-типа период колебаний можно найти из формулы

.

.

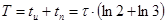

Для реализации автоколебательного мультивибратора на базе логических элементов КМОП-типа широко применяется схема, представленная на рис. 3.12.

Рис. 3.12. Схема мультивибратора на базе элементов КМОП-типа.

Рассмотрим принцип работы схемы. Пусть в исходном состоянии на входе ЛЭ1 - логический нуль, на выходе ЛЭ1 - логическая единица и на выходе ЛЭ2 - логический нуль. Напомним, что для элементов КМОП-типа характерно:  ,

,  и

и  . Тогда схему подключения RC-цепочки можно изобразить в виде, представленном на рис. 3.13, а.

. Тогда схему подключения RC-цепочки можно изобразить в виде, представленном на рис. 3.13, а.

а) б)

Рис. 3.13. Эквивалентные схемы подключения RC-цепи в мультивибраторе на базе элементов КМОП-типа.

Напряжение на конденсаторе стремится к + E и в момент времени t 1 напряжение на конденсаторе, а значит и на входе ЛЭ1 достигает значения  (рис. 3.14). При этом на выходе ЛЭ1 появляется логический нуль, а на выходе ЛЭ2 - логическая единица. Исходная схема теперь вырождается в схему, представленную на рис. 3.13, б. При этом начальное напряжение на конденсаторе будет

(рис. 3.14). При этом на выходе ЛЭ1 появляется логический нуль, а на выходе ЛЭ2 - логическая единица. Исходная схема теперь вырождается в схему, представленную на рис. 3.13, б. При этом начальное напряжение на конденсаторе будет  . Таким образом, значение напряжения на входе ЛЭ1 скачком возрастает до значения 1,5×E. После этого напряжение на R стремится к нулю. В момент t 2 напряжение на нем, а следовательно и на входе ЛЭ1 уменьшится до значения

. Таким образом, значение напряжения на входе ЛЭ1 скачком возрастает до значения 1,5×E. После этого напряжение на R стремится к нулю. В момент t 2 напряжение на нем, а следовательно и на входе ЛЭ1 уменьшится до значения  , что приведет к появлению на выходе ЛЭ1 логической единицы. На выходе ЛЭ2 соответственно появится логический нуль и схема снова примет вид, представленный на рис. 3.13, а. При этом конденсатор окажется подключенным в обратной полярности, т.е.

, что приведет к появлению на выходе ЛЭ1 логической единицы. На выходе ЛЭ2 соответственно появится логический нуль и схема снова примет вид, представленный на рис. 3.13, а. При этом конденсатор окажется подключенным в обратной полярности, т.е.  . Через защитный диод на входе микросхемы КМОП-типа конденсатор быстро разряжается до нуля. Таким образом, начальное значение напряжения на конденсаторе принимается равным нулю. Далее конденсатор начинает заряжаться до значения E с постоянной времени

. Через защитный диод на входе микросхемы КМОП-типа конденсатор быстро разряжается до нуля. Таким образом, начальное значение напряжения на конденсаторе принимается равным нулю. Далее конденсатор начинает заряжаться до значения E с постоянной времени  . Очевиден колебательный процесс, для которого можно записать

. Очевиден колебательный процесс, для которого можно записать

,

,

,

,

.

.

Рис. 3.14. Временная диаграмма работы мультивибратора на базе логических элементов КМОП-типа.

Приведенные схемы мультивибраторов на базе логических элементов и RC-цепей характеризуются невысокой стабильностью частоты генерируемых импульсов. Связано это как с большим технологическим разбросом параметров резисторов, конденсаторов и логических элементов, так и с условиями эксплуатации схемы. Кроме того, существенное влияние оказывают и процессы старения элементной базы. Точность генерируемой частоты в таких схемах обычно не превышает 10 %, что объясняется относительной погрешностью входящих в схему элементов. В большинстве же случаев требуется высокая точность установки частоты и стабильность ее в процессе эксплуатации. Наиболее простым решением данной задачи является использование кварцевых резонаторов, разброс параметров которых может составлять тысячные доли процента.

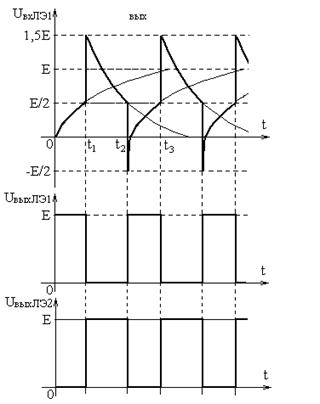

Вариант одной из схем мультивибратора с кварцевой стабилизацией частоты приведен на рис. 3.15. В основе ее лежит уже рассмотренный мультивибратор на базе RC-цепи и логических элементов КМОП-типа. Частота генерируемых импульсов определяется частотой кварцевого резонатора G. Переменный конденсатор C позволяет в незначительных пределах подстраивать частоту. Резистор R практически не влияет на частоту импульсов, но его номинал необходимо подбирать из условия надежного запуска мультвибратора. Кроме того, для более качественной формы выходных прямоугольных импульсов, в схему добавлен дополнительный буферный логический элемент ЛЭ3.

Рис. 3.15. Схема мультивибратора с кварцевой стабилизацией частоты.

3-4. Импульсные генераторы на интегральных таймерах.

На практике для формирования импульсных сигналов часто используются интегральные таймеры. Таймер формирует одиночные импульсы или последовательности импульсов с регулируемыми длительностью, скважностью и частотой. Таймеры делятся на два крупных класса: однотактные и многотактные. Однотактные таймеры предназначены для формирования импульсных сигналов с временными характеристиками в диапазоне от микросекунд до нескольких часов.

Структура однотактного таймера содержит обычно внешнюю (реже внутреннюю) времязадающую RC-цепь, внутренние пороговое устройство в виде аналогового компаратора и цифровую схему, фиксирующую состояние компаратора и формирующую на выходе напряжения низкого и высокого уровней. Многотактные таймеры состоят, как правило, из однотактного таймера, задающего базовую частоту, и счетчика, осуществляющего деление частоты однотактного таймера на фиксированное или произвольно задаваемое число. Поэтому, многотактные таймеры характеризуются сверхнизкими частотами и сверхпродолжительными временными характеристиками генерируемых импульсных сигналов. Многотактные таймеры с произвольно выбираемым коэффициентом деления частоты называются программируемыми, а с фиксированным коэффициентом деления – специализированными.

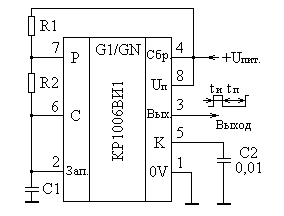

В качестве примера однотактного таймера рассмотрим интегральный таймер КР1006ВИ1, широко применяемый при разработке электронных устройств как в отечественной промышленности, так и за рубежом (зарубежный аналог - серия 555). Таймер конструктивно выполнен в пластмассовом корпусе DIP-8 (или 201.8-1 по ГОСТ 17467-72) с восемью выводами. Таймер имеет напряжения питания от 5 до 15 В, ток нагрузки до 100 мА и длительность формируемых импульсов от нескольких микросекунд до десятков минут.

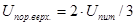

Структура таймера представлена на рис. 3.16. В состав таймера входят два компаратора - DA 1 – верхнего уровня, DA 2 – нижнего уровня. Делители на резисторах R 1, R 2 и R 3, имеющие одинаковые номиналы, задают пороги срабатывания  компаратора DA 1 и

компаратора DA 1 и  компаратора DA 2. Выходы компараторов соединены с цифровой схемой DD 1 фиксации состояния компараторов, роль которой выполняет асинхронный RS -триггер (триггеры будут рассмотрены в теме 5). Триггер также снабжен входом сброса

компаратора DA 2. Выходы компараторов соединены с цифровой схемой DD 1 фиксации состояния компараторов, роль которой выполняет асинхронный RS -триггер (триггеры будут рассмотрены в теме 5). Триггер также снабжен входом сброса  для установки на его выходе логического нуля и приведения таймера в исходное состояние. Для повышения нагрузочной способности микросхемы импульсы с выхода триггера усиливаются усилителем мощности DA 3. С выхода триггера сигнал подается на транзисторный ключ VT 1, обеспечивающий режим разряда конденсатора во времязадающей RC-цепи после срабатывания одного из компараторов и установления на выходе триггера напряжения логической единицы.

для установки на его выходе логического нуля и приведения таймера в исходное состояние. Для повышения нагрузочной способности микросхемы импульсы с выхода триггера усиливаются усилителем мощности DA 3. С выхода триггера сигнал подается на транзисторный ключ VT 1, обеспечивающий режим разряда конденсатора во времязадающей RC-цепи после срабатывания одного из компараторов и установления на выходе триггера напряжения логической единицы.

Рис. 3.16. Структура интегрального таймера КР1006ВИ1.

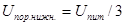

Рассмотрим некоторые типовые схемы включения таймера КР1006ВИ1. На рис. 3.17 приведена схема ждущего мультивибратора. При этом таймер запускается логическим нулем на входе 2, выходной импульс снимается с выхода 3 и длительность импульса определяется как

.

.

Рис. 3.17. Включение КР1006ВИ1 в режиме ждущего мультивибратора.

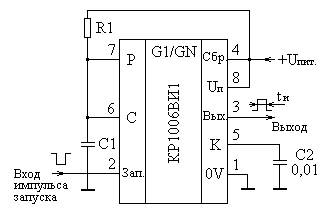

На рис. 3.18 приведена схема автоколебательного мультивибратора. Длительности импульса и паузы генерируемой последовательности импульсов определяется значениями R 1 и R 2

,

,

.

.

При этом для стабильной работы схемы необходимо, чтобы R 1+ R 2 не превышало 10 МОм при Uпит =15 В и 3 МОм при Uпит =5 В. Минимальное значение R 1+ R 2 составляет 2 кОм.

Рис. 3.18. Включение КР1006ВИ1 в режиме автоколебательного мультивибратора.

Контрольные вопросы.

1. Объясните назначение последовательной цепи из резистора Rогр и диода VD в схеме задержки на основе интегрирующей RC-цепи и логических элементов.

2. Выведите формулу для расчета tзад 2 схемы задержки на основе интегрирующей RC-цепи и логических элементов КМОП-типа.

3. Чем объясняется наличие тока через резистор R при отсутствии входного воздействия на схему задержки на основе дифференцирующей RC-цепи и логического элемента ТТЛ-типа?

4. Какую функцию выполняет эмиттерный повторитель в схеме ждущего мультивибратора?

5. Опишите принцип работы схем автоколебательных мультвибраторов.

6. Чем объясняется невысокая стабильность частотных характеристик мультивибраторов на базе RC-цепей?

7. Каков принцип построения многотатктных таймеров?

2014-02-09

2014-02-09 5020

5020