В большей части современных цифровых устройств используются микросхемы на МОП-структурах. Эта популярность обусловлена высоким быстродействием при низкой потребляемой мощности особенно в статическом режиме, высокой технологичностью изготовления. Эти микросхемы названы так потому, что их работа основана на регулировании величины тока в приповерхностном слое полупроводникового материала за счет влияния поперечного электрического поля на проводимость канала, т. е. здесь используются полевые транзисторы. Практическое применение получили полевые транзисторы с индуцируемым каналом с оксидной изоляцией затворов, образующие структуру металл-окисел-полупроводник (МОП), и транзисторы с комбинированной нитридно-оксидной изоляцией. Последние используются в запоминающих устройствах. В отличие от биполярных ток в канале создается основными носителями, что обуславливает их высокое быстродействие, т. к. процессы рассасывания носителей заряда в этих приборах отсутствуют.

Существуют полевые транзисторы с каналами n -типа и p -типа. Существуют и достаточно широко используются устройства трех типов: статического, квазистатического и динамического типов. В схемах квазистатического и динамического типов используется свойство высокого входного сопротивления МОП транзисторов, откуда вытекает способность емкости затвора длительное время сохранять заряд и уровень напряжения на затворе. Схемы этого типа широко применялись для построения последовательностных устройств: триггеров, регистров, счетчиков. В настоящее время наиболее часто используются схемы статического типа.

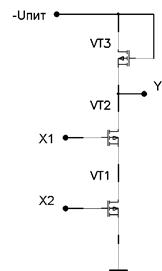

На рис. 4.7 приведена схема электрическая принципиальная базового элемента И-НЕ на р -канальных МОП-транзисторах.

Рис. 4.7. Схема электрическая принципиальная элемента 2И-НЕ

на р -канальных МОП-транзисторах.

Для реализации функции И-НЕ ключевые транзисторы VT1, VT2 включены последовательно с нагрузочным транзистором VT3. При наличии логических «1» на входах Х1, Х2 ключевые транзисторы VT1, VT2 открываются, через нагрузочный транзистор VT3 протекает ток, а на выходе Y устанавливается логический «0» (отрицательное напряжение близкое к 0). При наличии хотя бы одного логического «0» на входах Х1, Х2 ток в последовательно соединенных транзисторах не протекает и на выходе Y устанавливается логическая «1» (отрицательное напряжение близкое к Uпит). Эти схемы являются схемами отрицательной логики, т. к. логической «1» соответствует отрицательное напряжение на логических входах. Учитывая очень высокое входное сопротивление входных ключей (более 10 Ом), цифровые устройства на их основе имеют очень высокую нагрузочную способность (более 20). Такое построение логических элементов имеет существенные недостатки:

Ом), цифровые устройства на их основе имеют очень высокую нагрузочную способность (более 20). Такое построение логических элементов имеет существенные недостатки:

- невысокое быстродействие, т. к. эквивалентное сопротивление нагрузочного транзистора составляет ~ 30 кОм, а емкость нагрузки при 10 подключенных входах составляет ~ 20 пФ, что обуславливает минимальное время задержки ~ 0,5 мкс;

- постоянное протекание тока при логическом «0» на выходе.

- для сопряжения с микросхемами серий ТТЛ(ТТЛШ) требуются специальные преобразователи уровней.

Основным достоинством является технологическая простота изготовления этих микросхем, т. к. они содержат всего лишь один элемент – полевой транзистор. Ограничения по быстродействию, характерные для МОП схем с р- каналами, могут быть частично устранены с помощью использования в схемах n -канальных МОП структур. Подвижность электронов в полупроводнике больше, чем подвижность дырок, поэтому скорость переключения вентилей на n -канальных МОП транзисторах в 2-3 раза больше. К тому же логические уровни и напряжения питания у них такие же, как у ТТЛ.

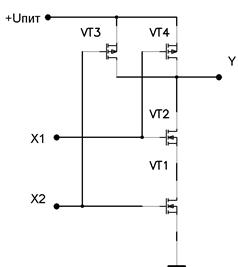

Дальнейшее совершенствование цифровой техники на МОП структурах привело к появлению комплементарных МОП (КМОП) элементов. На рис. 4.8 приведена схема электрическая принципиальная базового элемента И-НЕ на комплементарных МОП-транзисторах.

Как видно из схемы на рис. 4.8, здесь параллельно включены транзисторы р -типа и последовательно транзисторы n -типа. При подаче на любой из входов напряжения логического «0» соответствующий транзистор (VT1 или VT2) закрывается, при этом VT3 или VT4 открывается.

Рис. 4.8. Схема электрическая принципиальная элемента 2И-НЕ на

КМОП-транзисторах.

При этом на выходе микросхемы устанавливается уровень логической «1». При одновременном наличии на обоих входах логической «1», транзисторы VT1 и VT2 открыты, а VT3 и VT4 закрыты. При этом на выходе микросхемы устанавливается уровень логического «0». Ток через транзисторы протекает только при изменении логического состояния для перезаряда емкости, образованной емкостями входов, подключенных к выходу и емкостью монтажа.

В статическом состоянии потребляемый ток очень мал и определяется только сквозными токами утечки транзисторов. С другой стороны выходное сопротивление элемента невелико, что обуславливает высокое быстродействие устройства. В настоящее время созданы элементы, имеющие времена задержки единицы нс.

Рассмотренная структура КМОП логического элемента в настоящее время является наиболее часто используемой в цифровой технике. Следует отметить, что рассмотренный КМОП элемент относится к положительной логике. Причем для большинства типов КМОП возможно совместное использование с ТТЛ (ТТЛШ) микросхемами без специальных устройств согласования, т. к. они имеют те же величины напряжений логических уровней и напряжений питания.

2014-02-13

2014-02-13 4072

4072