Микросхема динамической памяти состоит из миллионов элементов, каждый из которых хранит всего один бит информации. На физическом уровне элементы памяти объединяются в прямоугольную матрицу, горизонтальные линейки элементов называются строками (ROW), а вертикальные - столбцами (Column).

Элементы всей строки матрицы могут считываться в современных микросхемах динамической памяти в буферный регистр - этот набор ячеек принято называть страницей (Page). Из-за высокой интеграции микросхем памяти становится невозможным обратиться к ячейке памяти, установив на шине адреса адрес ячейки памяти полностью. Слишком много разрядов должна иметь эта шина. Поэтому шину адреса делают в два раза уже и устанавливают адрес дважды. Сначала адрес строки, затем адрес столбца. Чтобы различать, установка какой части адреса происходит вводятся дополнительные сигналы управления RAS и CAS. Адрес строки передается по шине адреса и принимается в регистр адреса строки микросхемы памяти по спаду импульса RAS (Row Access Strobe). Адрес колонки передается по этой же шине и принимается в регистр адреса колонки микросхемы памяти по спаду импульса CAS (Column Access Strobe). На пересечении линии строки и колонки находится элемент памяти.

Поскольку обращение (запись или чтение) к различным ячейкам памяти обычно происходит в случайном порядке, то для поддержания сохранности данных производится регулярная регенерация (Memory Refresh - "освежение" памяти) - регулярный циклический перебор ячеек памяти с холостыми циклами перезаписи. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек.

Если динамическая память используется в видеобуферах графических адаптеров, то специальных циклов регенерации такая память не требует т.к. частота ее чтения для воспроизведения изображения на экране видеомонитора вполне достаточна для сохранения информации при чтении и сопровождающей чтение перезаписи.

Частоту регенерации можно определить следующим образом, если ток утечки составляет 0.1 нА, а емкость конденсатора порядка 0,1 пф, время разряда конденсатора на 1 вольт произойдет за время t порядка одной миллисекунды. Если считать такое падение напряжения максимально допустимым, то для выдачи состояния низкого или высокого уровня необходимо осуществлять периодическое восстановление информации (или ее регенерацию) с периодом t ref <=1мс. Таким образом, максимальный период обращения к каждой строке TRF (refresh time) для гарантированного сохранения информации должен быть менее 1мс.

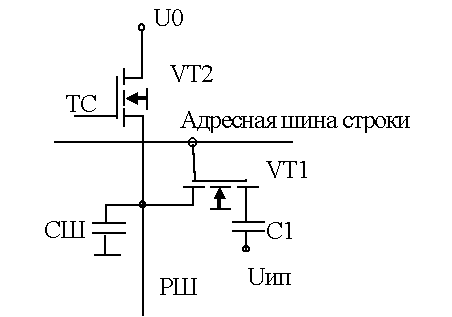

Микросхемы динамической памяти строятся на основе биполярных МОП- транзисторов. Элемент динамической памяти на МОП- структурах показан на рис.1.

В основе запоминающего элемента лежит один конденсатор С1 и один МОП- транзистор VT1. На схеме конденсатор показан в виде отдельного элемента, хотя реально его функции выполняет емкость затвор-подложка. Транзистор VT2 открывается сигналом ТС=1 и от источника U0 емкость СШ заряжается до напряжения U0.

Рис.1. Элемент динамической памяти на МОП- структурах.

При выборке данных транзистор VT1 выполняет функции ключа: при подаче сигнала на шину адреса строки он открывается и соединяет запоминающий конденсатор С1 с шиной столбца РШ (разрядной шиной). Емкость запоминающего конденсатора 0.1-0.2 пф, что значительно меньше емкости конденсатора шины (СШ), поэтому возникает незначительное изменение потенциала шины, которое усиливается при считывании информации высокочувствительными дифференциальными усилителями.

На вход дифференциального усилителя подается напряжение разрядной шины и опорное напряжение для определения разности. Опорный элемент построен аналогично запоминающему, он поддерживает опорное напряжение U0. В каждом столбце матрицы памяти расположены усилители, к которым подключаются элементы памяти и элементы, поддерживающие опорное напряжение. Считан может быть сигнал только с одного элемента памяти столбца, ключи остальных элементов в это время закрыты, но открыты все элементы строки. При этом заряды всей строки поступают на усилители и через некоторое время могут быть считаны. Такая операция называется активизацией строки.

Сигнал с выхода чувствительного дифференциального усилителя подается на формирующий выходной сигнал триггер-усилитель, выполняющий также функции элемента, который автоматически осуществляет регенерацию информации. Еще раз подчеркнем, что регенерация информации в рассматриваемой схеме производится сразу во всей строке. Считывание информации происходит при при установке сигнала Read на шине управления, при директиве Write происходит запись информации. Пока строка остается активной, возможны считывание или запись и других ячеек памяти. После того, как истекает время активности строки происходит закрытие строки, которое сопровождается подзарядкой (Precharge) элементов памяти строки. Последующее считывание данных этой строки невозможно без ее повторной активизации (установки адреса строки).

Микросхема динамической памяти

Главные особенности микросхем динамической памяти заключаются в следующем:

- отсутствуют источники для питания элементов запоминающих ячеек;

- необходимы логические схемы, обеспечивающие регенерацию информации;

- максимально проста схема накопителя, обеспечивающая минимум занимаемой площади;

- мала потребляемая мощность, поскольку динамический запоминающий элемент не потребляет тока в отрезки времени, когда к нему не происходит обращение.

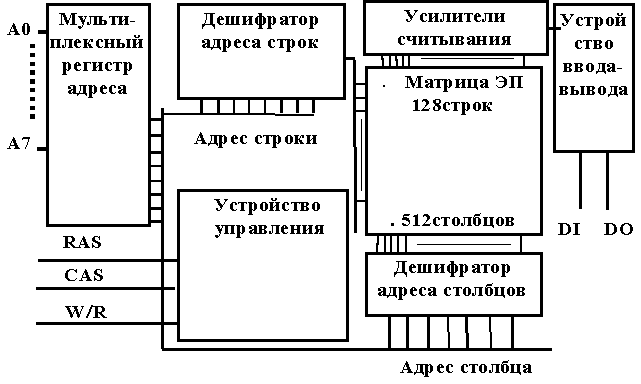

Для формирования внутренних сигналов, управляющих включением и выключением в определенной последовательности различных узлов микросхемы, в структуре микросхемы предусмотрена схема управления. Входные, выходные и управляющие сигналы микросхемы памяти: RAS (Row Adress Strobe) - строб адреса строки; CAS (Column Adress Strobe) - строб адреса столбца; WR (записьчтение); вход данных - DI; выход данных - DO. Микросхема имеет усилители считывания и регенерации в каждом столбце матрицы, регистр адреса, дешифраторы адреса строк и адреса столбцов, устройство управления и устройство ввода и вывода данных. Структура микросхемы приведена на рис.2.

Рис.2. Структура микросхемы динамической памяти

На линиях RAS (row address strobe - строб адреса строки) и CAS (column address strobe - строб адреса столбца) в спокойном состоянии поддерживается высокий уровень сигнала, что означает, что никакой информации на адресных линиях нет и никаких действий, связанных с чтением или записью данных. В случае строчной регенерации, регенерация информации осуществляется путем обращения к каждой строке динамической памяти перебором строчных адресов в любом режиме работы.

В современных микросхемах памяти регенерацию производит устройство регенерации, встроенное в микросхему памяти. Нарушение режима регенерации может привести к нарушению логических состояний микросхем памяти. Поэтому в схемах регенерации применяются защитные схемы, поддерживающие истинность логических состояний элементов матрицы микросхемы памяти совместно с генератором циклов регенерации.

Микросхема подключается к шине адреса и данных. Линии адреса служат для выбора адреса ячейки памяти, а линии данных - для чтения или записи данных в память.

Низкий уровень сигнала W/R готовит микросхему к считыванию состояния шины данных и записи полученной информации в соответствующую ячейку, а высокий, наоборот, заставляет считать содержимое ячейки и установить его на линиях шины данных. Использование одной и той же шины данных для вывода данных и для чтения данных позволяет в два раза уменьшить количество выводов шины данных. Это, как и уменьшение ширины шины адреса позволяет уменьшить размеры микросхемы, а значит, получить более высокие рабочие частоты.

Рассмотрим, какие факты мешают повышению рабочей частоты микросхемы памяти:

1. Скорости распространения электрических сигналов ограничены, поэтому длины проводников, подведенных к различным ножкам микросхемы, не должны сильно отличаться друг от друга, иначе сигнал от одного вывода будет опережать сигнал от другого.

2. Длины проводников не должны быть очень велики, задержка распространения сигнала не позволит повысить быстродействие.

3. Любой проводник действует как приемная и как передающая антенна, создавая помехи. Уровень помех резко усиливается с ростом тактовой частоты.

4. Любой проводник обладает электрической емкостью. Чем больше емкость, тем меньше скорость передачи данных.

Совмещение выводов шины для вывода и ввода данных увеличивает скорость обмена с памятью, но не позволяет осуществлять чтение и запись одновременно.

Интересно, что в первых компьютерах специальная схема приостанавливала (прерывала) работу процессора на время регенерации, для управления процессом регенерации.

На рис.2 приведена микросхема асинхронной динамической памяти, в которой разрядность данных - 1 бит. Далее мы узнаем как совершенствовалась память и чем отличается синхронная динамическая память от асинхронной. А сейчас поговорим об организации микросхем памяти и построении модулей памяти.

Микросхемы памяти могут иметь и другую организацию. Например, распространенные (2006г.) микросхемы (чипы) синхронной динамической памяти DDR SDRAM фирмы Samsung: K 4 H 5 6 0 8 3 8 E — T C B 3 (рис.3) имеют емкость 36 мегабайт (256 мегабит). Адресуемая ячейка памяти чипа 8 битная.

Рис.3. Микросхема памяти DDR SDRAM фирмы Samsung

Для того, чтобы исключить ожидания при регенерации считанных данных, современные микросхемы памяти имеют несколько матриц. Последовательные обращения к данным при чтении будут происходить без задержек, если последовательные ячейки памяти расположены на разных матрицах. Таким образом можно избежать задержек на регенерацию при чтении последовательных данных. Рассматриваемая нами микросхема имеет 4 матрицы (допускает при построении модуля памяти использование четырех банков памяти).

2014-09-02

2014-09-02 2143

2143