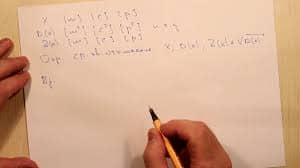

Целью системы сбора и обработки данных (СОД) является получение информации о состоянии объекта и рациональная организация процессов управления, контроля, и измерения с высокими качествами характеристики.

Рисунок 22 - Структура системы сбора и обработки данных

P1…Pn – обмен первичной информации

С1…Cn – сигналы, описывающие внутреннее состояние объекта

R1…Rn – сигналы внутреннего состояния объекта

Функции СОД можно описать следующими системами уравнений:

C1 =F1(Р1,Р2…. Рm, R1 …..Rk)

C2 =F2(Р1,Р2…. Рm, R1 …..Rk)

….. (1)

Cn =Fn(Р1,Р2…. Рm, R1 …..Rk)

F – функция алгоритма управления

P1 =f1(C1,C2…. Cn, R1 …..Rk)

P2 =f2(C1,C2…. Cn, R1 …..Rk)

…. (2)

Pm =fm(C1,C2…. Cn, R1 …..Rk)

f – внешнее проявление внутреннего состояния объекта, то есть функция контроля.

R1 =φ1(P1,P2…. Pm)

R2 = φ 2(P1,P2…. Pm)

…. (3)

Rk = φ k(P1,P2…. Pm)

φ – функция контроля и самотестирования СОД.

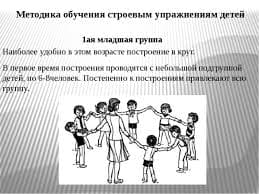

Микропроцессорная система сбора и обработки данных имеет столько каналов, сколько информации он считывает, собирает и обрабатывает. Так как информация, в основном, имеет природный характер (налоговый), то самым трудоемким процессом является канал аналого-цифрового преобразования АЦП. На рисунке 23 представлена структурная схема системы сбора и обработки с АЦП по каждому каналу информации.

Рисунок 23 - Структуры СОД

Обозначения на схеме:

Д – датчик;

СУ – согласующее устройство;

СН – система нормирования;

ФП – функциональный преобразователь;

АЦП – аналого-цифровой преобразователь;

ЦМ - цифровой мультиплексор;

МП – микропроцессор;

Структура СОД разделяются по тому, где расположен АЦП. На рисунке 23 АЦП расположен на каждом канале, это дороже, но надежней. Если АЦП стоит один общий на нескольких каналах (рисунки 24 и 25), то скорость преобразования падает. Надежность зависит от того, будет ли выборка и хранение каждого канала происходить отдельно, или это будет общая выборка. Тогда надежность системы зависит от надежности аналогового мультиплексора. Даже при высоконадежной схеме, рисунок 23, количество входов цифровых каналов ограничено значением допустимой ошибки.

Nц <= ∆Хiдоп / [(dXi / dt)max* tk];

В простейшем случае схема выглядит следующим образом:

Количество аналоговых каналов ограничивается допустимой ошибкой и временем преобразования tp, tk – период коммутации.

Nа <= ∆Хiдоп / [(dXi / dt)max* (tk+ tp)];

dXi / dt - допустимая скорость изменения аналогового сигнала по i-каналу.

СПЛК в качестве цифрового регулятора является автономным устройством, в нем уже заложены алгоритмы управления и регулирования. Если сигнал из датчиков аналоговые, то основное время уходит на АЦП.

2015-02-04

2015-02-04 3539

3539