Компилятор предоставляет очень широкие возможности управления алгоритмом компиляции посредством опций меню. В этой работе рассмотрим лишь некоторые возможности (подробнее об этом можно прочитать в руководстве пользователя):

· автоматический или ручной выбор ПЛИС;

· автоматическое разбиение (при необходимости) на несколько корпусов ПЛИС;

· возможность назначения сигналов на конкретные выводы микросхемы;

· возможность размещения конкретных функций в конкретных ресурсах микросхемы;

· оптимизация алгоритмов синтеза;

· временной синтез (с учетом требуемых временных параметров);

· возможность управления соотношением потребление / быстродействие;

· удобная система отслеживания синтаксических и семантических ошибок.

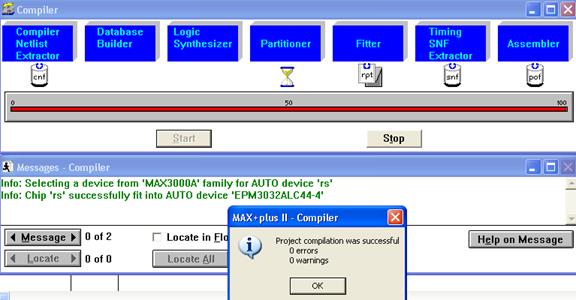

1.3.4.1 После создания графического и сигнального файлов необходимо откомпилировать наш проект. Для этого откроем окно компилятора (рис. 1.20) Compiler ( ) (или меню MAX+plus II/Compiler) и нажмем кнопку Start для начала компиляции проекта.

) (или меню MAX+plus II/Compiler) и нажмем кнопку Start для начала компиляции проекта.

|

Рис. 1.20 Окно компилятора

Если наш проект не имеет ошибок, то после компиляции будет следующее рис. 1.21.

Рис. 1.21 Окна проекта после компиляции

Компиляция проекта производиться затем, чтобы преобразовать схему в удобный для машины язык. Далее откомпилированная программа выполняется. При внесении каких-либо изменений в проект РЕКОМЕНДУЕТСЯ заново его откомпилировать, т.к. только после компиляции все изменения вступят в силу.

Все операции симуляции, анализ задержек, размещение элементов на микросхеме выполняются только после компиляции и проверки ошибок, которая осуществляется во время компиляции.

1.3.4.2 Временные диаграммы отображают как логику функционирования, так и реальные временные соотношения сигналов, гонки (состязания). Моделирование осуществляется с высокой степенью адекватности, что существенно упрощает процесс отладки устройства. В случае успешной компиляции возможен временной анализ, для чего следует выполнить следующее.

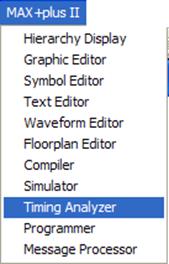

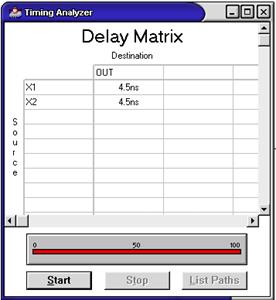

1.3.4.3 После проведения компиляции посмотрим временные задержки между входом и выходом. Для проведения временного анализа задержек необходимо выбрать меню MAX+plus II/TimingAnalyzer (рис. 1.22) и нажать кнопку Start (см. рис. 1.23).

Рис. 1.22 Выбор подпрограммы анализа задержек

Рассчитанные задержки Рассчитанные задержки |

Рис. 1.23 Окно анализатора задержек

Для запуска подпрограммы анализа задержек необходимо нажать кнопку Start. По строкам отображается информация о входных сигналах, в столбце о выходном. Таблица представляет собой перекрестную таблицу, показывающую время, через которое сигнал, поданный на вход, вызовет реакцию на выходе (например, в нашем случае 4,5ns - задержка сигнала на выходе относительно входа).

1.3.4.4 После этого необходимо отсимулировать наш проект. Для проведения симуляции необходимо выбрать меню MAX+plus II/Simulator или иконка Simulator  . Затем нажать кнопку Start. После успешной симуляции мы увидим следующее (см. рис. 1.24).

. Затем нажать кнопку Start. После успешной симуляции мы увидим следующее (см. рис. 1.24).

|

Рис. 1.24 Окно симулятора

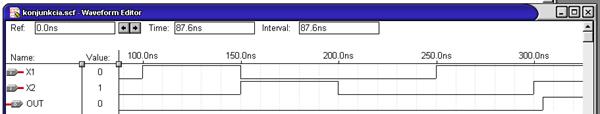

Результатом работы схемы является рис. 1.25.

Рис. 1.25 Результат работы схемы в сигнальном файле

Waveform Editor

После получения результата работы схемы нам необходимо описать программно схему, собранную в графическом редакторе (рис. 1.14). Программа будет написана на языке проектирования цифровых устройств AHDL.

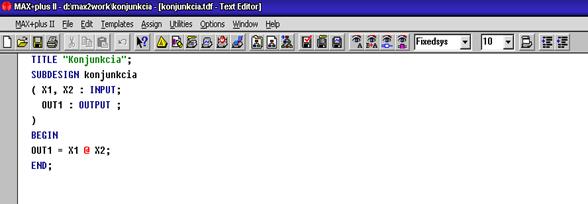

1.3.4.5. Пример программы на языке AHDL, реализующей функцию конъюнкции (рис. 1.26):

Рис. 1.26 Программа, реализующая функцию конъюнкции

Для написания программы, описывающей работу комбинационных схем необходимо создать новый текстовый файл в меню File/New… выбрать Text Editor File и нажать ОК.

После того, как создан новый текстовый файл, появляется окно, в котором будет написана программа. Программа делится на несколько частей. Она начинается с заголовка TITLE. Это необязательная часть программы, ее можно не включать в текст программы. В заголовке обычно указывается название программы, или какой-нибудь комментарий к ней. После заголовка TITLE ставится знак «точка с запятой». За заголовком TITLE идет обязательная часть программы SUBDESIGN. Это переводится как подмодель или как подсхема. Этот раздел заключается в круглые скобки. Необходимо, чтобы имя вашей подмодели, в данном случае это Konjunkcia, обязательно совпадало с тем именем, под которым вы сохраните свою программу. Т.е. если программа будет сохранена под именем, скажем KON_junkcia или Konjunk, вместо Konjunkcia, то она работать не будет. В заголовке SUBDESIGN описываются имена входов и выходов схемы. Имена входов обозначаются словом INPUT, и отделяются от их названий символом «двоеточия», а имена выходов обозначаются словом OUTPUT соответственно. Сами же названия входов и выходов обозначаются символьными именами или буквами. Каждая написанная в программе строчка завершается символом «;». После раздела SUBDESIGN следует обязательная часть программы – тело программы, которое начинается со слова BEGIN. В данном разделе производятся все возможные логические и арифметические операции над входами и выходами, переменными, массивами и т.п. Тело программы, и сама программа заканчивается словом END, после которого ставится «точка с запятой». Программа для логического И (конъюнкция) представлена выше.

После создания текстового файла, необходимо сохранить файл File/Save As…. Задать имя нашего файла. В меню File/Project/Name выбратьсозданный нами текстовый файл, для того чтобы выполняемый нами проект стал текущим и компилировался именно он.

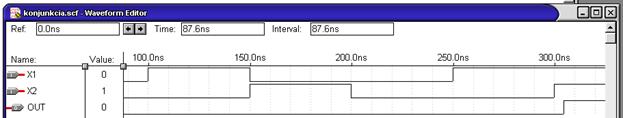

1.3.4.6 Когда мы написали программу на языке AHDL, нам необходимо создать сигнальный файл (см. рис. 1.16). Задать последовательность сигналов на вход, сохранить сигнальный файл File/Save As…,откомпилировать наш проект на наличие ошибок (см. п. 1.3.4.1), сделать анализ временных задержек (см. п. 1.3.4.3), а затем симулировать наш проект (см. п. 1.3.4.4). Результатом выполнения нашего проекта будет служить выходная диаграмма, отображенная в сигнальном файле рис. 1.27.

Рис. 1.27 Результат выполнения проекта (выполнение программы на языке AHDL)

Таким образом, выполнение лабораторной работы сводится к синтезу комбинационных схем в пакете Multisim, снятию временных диаграмм в этом пакете. Построению комбинационных схем в пакете MAX+plus II, получению временных диаграмм с временными задержками между входом и выходом, а также написанию программ на языке проектированию цифровых устройств AHDL в пакете MAX+plus II и при выполнении данных программ – получение диаграмм с анализом временных задержек.

Контрольные вопросы

1. Синтезируйте схему, реализующую функцию «запрета по X1».

2. Синтезируйте схему, реализующую функцию «запрета по X2».

3. Синтезируйте схему, реализующую функцию «сумма по модулю два».

4. Синтезируйте схему, реализующую функцию «штрих Шеффера».

5. Синтезируйте схему, реализующую функцию «стрелка Пирса».

6. Синтезируйте схему, реализующую функцию «инверсия по X1».

7. Синтезируйте схему, реализующую функцию «инверсия по X2».

8. Синтезируйте схему, реализующую функцию «дизъюнкция».

9. Синтезируйте схему, реализующую функцию «исключающее ИЛИ».

10. Синтезируйте схему, реализующую функцию «логическая равнозначность».

11. Синтезируйте схему, реализующую функцию «импликация от X1».

12. Синтезируйте схему, реализующую функцию «импликация от X2».

13. Синтезируйте схему, заданную функцией трех переменных

14. Синтезируйте схему, заданную функцией четырех переменных

15. Синтезируйте схему, заданную диаграммой Вейча

X1

X1

X2

X3

X3

16. Синтезируйте схему, заданную функцией двух переменных

2015-05-10

2015-05-10 820

820