Триггеры позволяют также строить линии задержки цифровых сигналов, для чего несколько триггеров соединяется в последовательную цепочку, причем все они тактируются единым тактовым сигналом С. Такое включение позволяет, например, одновременно обрабатывать комбинационными схемами несколько последовательных во времени состояний какого-то одного сигнала.

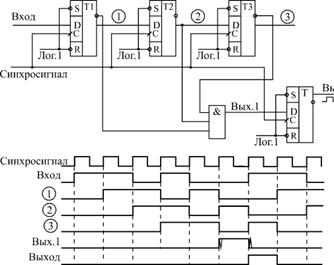

В качестве примера на рис. 3.22 приведена схема, которая выделяет во входном сигнале 3-х тактовую последовательность 010. Цепочка из трех триггеров Т1, Т2 и Т3, тактируемых единым синхросигналом, запоминает три последовательных состояния входного сигнала. Например, если на выходе триггера Т2 будет зафиксировано состояние входного сигнала в N-ом такте, то на выходе триггера Т1 будет состояние входного сигнала в такте (N+1), а на выходе триггера Т3 — в такте (N–1). Из-за конечной величины задержки переключения триггеров в каждый следующий триггер входной сигнал будет переписываться еще до того как он поменяет свое значение вследствие переключения предыдущего триггера.

Рис. 3.22 Выделение 3-тактовой последовательности тактов во входном сигнале

Подавая выходные сигналы триггеров (прямые или инверсные в зависимости от нужных уровней) на элемент И с нужным числом входов, можно зафиксировать любую 3-х тактовую последовательность во входном сигнале. Для предотвращения появления паразитных импульсов в выходном сигнале (они возможны, так как входные сигналы элемента И изменяются почти одновременно) применяется выходной триггер Т, тактируемый тем же самым общим синхросигналом. На выходе триггера Т получаем единичный сигнал, соответствующий последовательности 010 во входном сигнале. Правда, этот выходной сигнал будет задержан относительно конца выделяемой последовательности 010 на два такта.

Контрольные вопросы

- Что такое триггер?

- Какие выходы имеет триггер?

- Какие бывают триггеры по способу записи?

- В какое состояние устанавливается триггер по входу S?

- В какое состояние устанавливается триггер по входу R?

- Как обозначается вход синхронизации?

- Как обозначается счетный вход?

- Нарисуйте условное обозначение -S-R триггера. Какая комбинация сигналов является запрещенной?

- Нарисуйте условное обозначение SR триггера. Какая комбинация сигналов является запрещенной?

- Нарисуйте схему -S-R триггера. Покажите на схеме, как триггер перебрасывается из состояния «1» в состояние «0».

- Нарисуйте схему SR триггера. Покажите на схеме, как триггер перебрасывается из состояния «1» в состояние «0».

- Нарисуйте условное обозначение JК триггера. Объясните по схеме особенности его работы.

- Напишите таблицу истинности Т триггера. Поясните по схеме принцип его работы.

- Объясните по схеме принцип работы Т триггера «мастер-помощник».

- Какой триггер называется синхронным.

- Поясните, используя Рис.3.15, переключение синхронного триггера SR из состояния «0» в состояние «1» с учетом состояний ЛЭ.

- Нарисуйте схему синхронного –S-R триггера на элементах ИЛИ-НЕ. Объясните его работу с помощью диаграммы.

- Нарисуйте схему преобразования JK триггера в триггер D.

- Нарисуйте схему преобразования JK триггера в триггер Т.

- Нарисуйте схему преобразования D триггера c установочными входами -R-Sв триггер RS.

2015-10-14

2015-10-14 2038

2038