Шифраторы это комбинационные устройства, выполняющие функции обратные дешифратору.

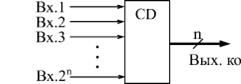

При подаче сигнала на один из его входов (унитарный код) на выходе образовывается соответствующий двоичный код. Следовательно, если число входов шифратора 2n, то число выходов – n.

Функциональная схема шифратора представлена на Рис. 6.13.

|

| Рис.6.13. Функциональная схема шифратора |

Шифраторы используются гораздо реже, чем дешифраторы. Это связано с более специфической областью их применения. Значительно меньше и выбор микросхем шифраторов в стандартных сериях.

Микросхемы шифраторов обозначаются CD, в отечественных сериях шифраторы имеют в названии буквы ИВ.

В Таблице 6.3. представлена таблица состояний шифратора на три выхода

| Таблица 6.3 | |||

| Вход I | Выходы | ||

| Y1 | Y2 | Y3 | |

Каждый из трех выходов описывается логическим выражением:

Y3 =Х4+Х5+Х6+Х7

Y2=Х2+Х3+Х6+Х7

Y1=Х1+Х3+Х5+Х7

Эти функции реализуются элементами ИЛИ на выходах которых формируется требуемый код.

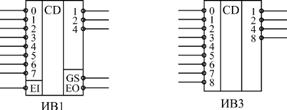

На рис. 6.14 показаны микросхемы шифраторов ИВ1 и ИВ5.

Микросхема ИВ1 имеет 8 входов и 3 выхода (шифратор 8–3).

Микросхема ИВ2 имеет 9 входов и 4 выхода (шифратор 9–4).

Все входы шифраторов - инверсные (активные входные сигналы — нулевые).

Все выходы тоже инверсные, то есть формируется инверсный код.

Микросхема ИВ1, помимо 8 информационных входов и 3 разрядов выходного кода (1, 2, 4), имеет инверсный вход разрешения –ЕI, выход признака прихода любого входного сигнала –GS, а также выход переноса –EO, позволяющий объединять несколько шифраторов для увеличения разрядности.

Рис. 6.14. Микросхемы шифраторов

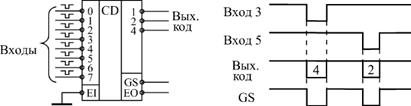

На Рис. 6.15 показаны стандартная схема включения шифратора и временные диаграммы его работы.

Рис. 6.15. Стандартное включение шифратора

Инверсия выходного кода приводит к тому, что при приходе нулевого входного сигнала на выходе формируется не нулевой код, а код 111, то есть 7. Точно так же при приходе, например, третьего входного сигнала на выходе образуется код 100, то есть 4, а при приходе пятого выходного сигнала — код 010, то есть 2.

Наличие у шифраторов входов EI и EO позволяет увеличивать количество входов и разрядов шифратора, правда, с помощью дополнительных элементов на выходе.

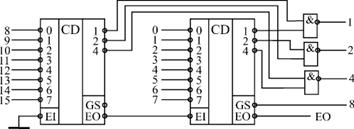

На рис. 6.16 показан пример построения шифратора 16–4 на двух микросхемах шифраторов ИВ1 и трех элементах 2И-НЕ.

Одновременное или почти одновременное изменение сигналов на входе шифратора приводит к появлению периодов неопределенности на выходах. Выходной код может на короткое время принимать значение, не соответствующее ни одному из входных сигна-

Рис. 6.16. Шифратор 16–4 на двух шифраторах 8–3

лов. Поэтому в тех случаях, когда входные сигналы могут приходить одновременно, необходима синхронизация выходного кода, например, с помощью разрешающего сигнала EI, который должен приходить только тогда, когда состояние неопределенности уже закончилось.

Контрольные вопросы

49. Что такое дешифратор?

50. Какой дешифратор называется полным?

51. Что такое унитарный код?

52. Объясните принцип построения линейного дешифратора.

53. Объясните принцип построения матричного дешифратора на функциональном уровне и на уровне логических элементов.

54. Объясните принцип построения пирамидального дешифратора.

55. От чего зависят сложность и быстродействие дешифраторов?

56. Как обозначается микросхема дешифратора?

57. Объясните принцип работы дешифратора на примере микросхемы ИД7.

58. Нарисуйте дешифратор 4-16 на микросхемах 2-4.

59. Что такое шифратор?

60. Как обозначается микросхема шифратора?

61. Объясните принцип работы шифратора на примере микросхемы ИВ1.

2015-10-14

2015-10-14 3395

3395