Випуск у жовтні 1998 року нової серії FРGА - Virteх значно розширив область застосування мікросхем FPGА. У першу чергу це торкнулося застосування FPGА Virtех як заміни в проектах замовлених спеціалізованих мікросхем (АSICs). Це стало можливо завдяки поліпшенням в архітектурі Virtех і застосуванні нових технологій виробництва "кремнію" (0.18мкм кМОН із шестишаровою металізацією). Нові технології дозволяють робити кристали ємністю до 3.2 мільйона системних вентилів, що працюють на

системних частотах до 311 МГц і дозволяють управляти тактовими сигналами всієї системи.

Для роботи в системах із високою продуктивністю в архітектурі FPGА серії Virtех передбачені дві функції: керування системними тактовими сигналами і функція вибору стандарту логічного сигналу блока вводу/виводу.

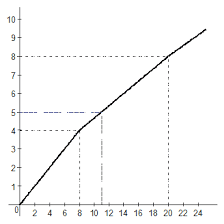

Одним із чинників обмежуючих швидкодію FPGА є затримка поширення тактового сигналу по кристалі. Ті ж проблеми з затримками виникають і на друкованих платах. Для рішення цієї проблеми на кристалі організовані спеціальні тактові модулі, що вирівнюють часові параметри елементів плати. Багато виробників мікросхем FPGА організують на кристалі модулі названі РLL (рhasе-Іоcked Іоор), що підбудовують часові параметри внутрішніх тактових ліній. Хіlіnх використовує модулі називані DLL(digital lelay-locked Іоор), що можуть бути використані для мінімізації як усередині кристальних затримок тактових сигналів так і тактових затримок на платі.

Кожний DLL-модуль може стабілізувати частоти до 320МГц. DLL-модуль має 6 виходів і може бути використаний для подвоєння або ділення частоти. Множення частоти на число більше 2-х досягається шляхом каскадування DLL-модулів, яких на кристалі знаходиться 4 (сімейство Virtех) або 8 (сімейство Virtех -Е). Перевага DLL перед PLL полягає у відсутності дребезгу фронтів.

Іншою проблемою при розробці високошвидкісних систем є застосування в системі різноманітних стандартів логічних сигналів і напруг живлення елементів системи. В даний час можна зустріти системи що одночасно складаються із елементів з напругою живлення 5В, 3.3В, 2.5В, 1.8В, які повинні сприймати і передавати сигнали один одному. Більшістю виробників ПЛИС FPGА для рішення даної проблеми застосовується метод при якому використовуються різноманітні напруги живлення логічного ядра і блоків вводу/виводу. Хіlіnх у серії Virtех застосовує більш досконалий метод - технологію 8е1ест/О, що дозволяє запрограмувати кожний блок

вводу/виводу на визначений стандарт. Технологія Virtex Select/О підтримує до 20 різноманітних стандартів.

Архітектура серії Virtex по організації логічних блоків і комутаційних ресурсів значно відрізняється від архітектури попередніх серій ПЛИС FPGА Хіііпх. Логічна комірка Virtex ідентична логічній комірці серій 8рагІап і ХС4000 і являє собою 4-й входовий функціональний генератор + D-тригер, але конфигурований логічний блок складається з 4-х комірок, а не з 2-х. У кристалі є декілька блоків ОЗП кожний по 4КБіти, також можлива реалізація 1ббіт пам'яті на кожному 4-и входовому функціональному генераторі.

Основні особливості сімейства Уігіех:

- програмовані користувачем логічні інтегральні схеми, що рекомендуються для заміни АSІС (арliсаtіоns specifiс integrated circuit- спеціалізована інтегральна схема)

- логічна ємність від 50К до 1М системних вентилів

- системна продуктивність до 200МГц

- підтримка функції Ноt-swар для Соmрасt РСІ

- технологія Virtex Select/О підтримує 17 різноманітних стандартів по вводу/виводу, серед котрих LVТТL, LVСМО82, РСІЗЗ_5, РСІ66_5, РСІЗЗ_3, РСІ66_3, GTL, GTL+, SSТL2(І), SSТL2(ІІ), SSТLЗ(І), SSТLЗ(ІІ), НSТL(І), НSТL(ІІ), НSТL(ПІ), АGР, СТТ

- чотири спеціальних схеми автопідстроювання затримок (DLL) для поліпшеного керування тактуванням.

- чотири основні мережі глобального розподілу сигналів тактування з малими розбігами фронтів, плюс 24 додаткові локальні тактові лінії

- ієрархічна 3-й рівнева система елементів пам'яті: реалізація на базі 4-й входового функціонального генератора (4-LUT –LookUp ТаbІе) конфигурує або як 16 бітову RАМ (Random

Ассеss Меmоrу), або як 16 бітову двопортову RАМ, або як 16-и бітовий регістр зсуву

- вмонтована блокова пам'ять, кожний блок конфігурується як 4К-біт синхронний двопортовий RАМ

- швидкі інтерфейси до зовнішньої високопродуктивної RАМ

- спеціальна логіка прискореного переносу для високошвидкісних арифметичних операцій

- спеціальна підтримка множників

- каскадує ланцюжки для функцій із великою кількістю входів

- велике число регістрів із дозволом тактування і синхронні/асинхронні ланцюги установки і скидання

- внутрішні шини з трьома станами

- логіка периферійного сканування у відповідності зі стандартом ІЕЕЕ1149.1

- підтримується системами проектування Foundation Sеrіеs і Аlliance Sеrіеs

- виготовляються за технологією 0.22мкм SRАМ кМОН із 5-й шаровою металізацією

- 100% фабричне тестування

2018-01-08

2018-01-08 384

384