Полусумматоры и сумматоры

Одними из основных элементов арифметико-логических устройств ЭВМ являются полусумматоры и сумматоры.

4.1.1 Сумматором называется комбинационный узел, который производит сложение двух многоразрядных чисел А и В, представленных в двоичной форме:

а m-1 …аi…а1а0; bm-1 …bi…b1b0

Основой многоразрядных сумматоров являются схемы одноразрядного полусумматора и полного сумматора.

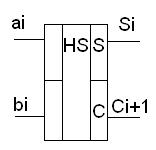

4.1.2 Одноразрядный полусумматор имеет 2 входа и 2 выхода, а одноразрядный сумматор 3 входа и 2 выхода (см.рис.4.1).

а) б)

где ai, bi – входы для сложения i разрядов чисел А и В;

Ci – вход переноса результата с предыдущего одноразрядного сумматора числа (Сi-1);

Si – выход результата сложения ai и bi;

Ci+1 – выход переноса результата сложения аi и bi.

Рисунок 4.1 - Условное обозначение одноразрядных полусумматора (а) и сумматора (б)

4.1.3 Рассмотрим таблицы истинности, логические функции и схемы построения полусумматоров и сумматоров.

В таблицах 1 и 2 приведены переключательные функции соответственно полусумматора и сумматора, соответствующие правилам двоичной арифметики.

4.1.4 На основании правил перехода от таблиц истинности к аналитической дизъюнктивной нормальной форме можно записать для полусумматора:

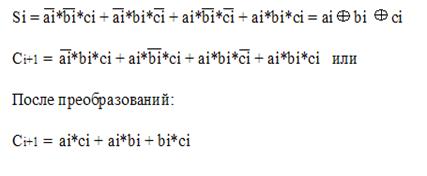

4.1.5 Для полного сумматора можно записать:

|  | ||

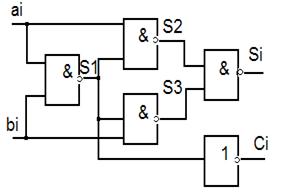

4.1.6 В соответствии с таблицей 1 два варианта схем полусумматоров представлены на рисунках 4.2 а) и б).

а) б)

Рисунок 4.2 – Схемы полусумматоров

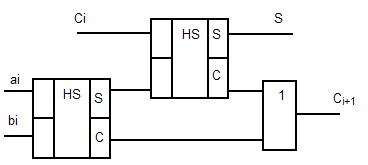

4.1.8 Схема полного сумматора можно составить из 2-х полусумматоров рисунок 4.3 (в соответствии со свойствами ассоциативности булевой алгебры)

Рисунок 4.3 - Схема полного сумматора, составленного из 2-х полусумматоров (в соответствии со свойствами ассоциативности булевой алгебры)

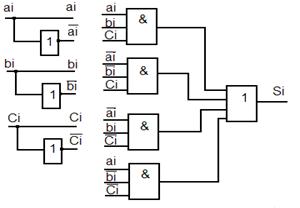

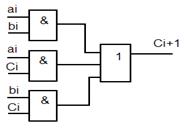

4.1.9 На рисунке 4.4 представлена схема полного сумматора на элементах НЕ, И, ИЛИ.

|  | ||

Рис. 4.4 Схема полного сумматора на элементах НЕ, И, ИЛИ

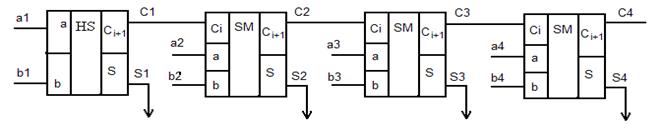

4.1.10 Для сложения 2-х полноразрядных чисел на каждый разряд требуется один полный сумматор, кроме первого (младшего) разряда, где необходим один полусумматор. Многоразрядные сумматоры строятся путем каскадного соединения одноразрядных сумматоров, как показано на рисунке 4.5.

Рисунок 4.5 - Четырехразрядный сумматор, составленный каскадным соединением полных сумматоров.

4.1.11 Каскадное соединение сумматоров с последовательным переносом обладают существенным недостатком – невысоким быстродействием, т.к. сигнал переноса Ci может появиться только после появления на входе i-го сумматора сигнала переноса с предшествующего разряда, т.е. с (i–1) – го.

Поэтому созданы ИМС сумматоров с параллельным и групповым переносом, в основе построения которых лежит схема ускоренного переноса, формирующая сигналы переноса параллельно с вычислением сигналов сумм в каждом разряде и непосредственно по значениям входных переменных.

2014-02-12

2014-02-12 1409

1409