Эмиттерно-связанная логика (ЭСЛ)

Основу этой группы ИМС составляет переключатель тока, представляющий собой ключевой элемент на транзисторах с объединенным эмиттером. Такие логические ИМС наиболее быстродействующие. Их конструкция здесь не рассматривается.

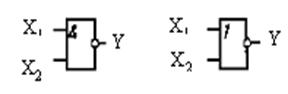

На рис.5.5 показано условное обозначение элементов И-НЕ, ИЛИ-НЕ,

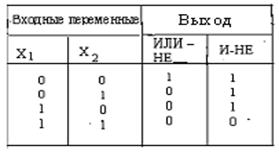

а в таблице 5.1 –соотношение между их входными и выходными сигналами.

|

|

Интегральная технология и использование методов алгебры логики позволили создать большое число различных триггеров на базе логических элементов, различающихся структурой цепей управления и режимами работы. Триггер состоит из цепей управления и запоминающих устройств и имеет один, два (или более) входа и два выхода. Каждый из входов имеет определенное функциональное назначение, которое отражается в обозначении данного входа (R, S, К, D и т. д.).

Цепи управления, в которые поступают входные (информационные) сигналы, преобразуют их в сигналы для запоминания и считывания.

Запоминающие устройства состоят из двух плеч, в каждом из которых одновременно хранятся сколь угодно долго два сигнала, один из которых соответствует логической 1, другой - логическому 0.

Выход триггера Q, с которого в исходном состоянии снимается высокий потенциал, обычно называют прямыми, другой - инверсным (обозначается `Q).

По способу записи информации все триггеры подразделяют на асинхронные, в которых информация записывается непосредственно при поступлении входного сигнала, и тактируемые (синхронные), записывающие входную информацию только при поступлении разрешающего тактового импульса.

Названия триггеров составляют из типов входов.

Рассмотрим примеры построения некоторых наиболее простых типов триггеров на базе логических элементов ИЛИ-НЕ, либо И-НЕ.

2014-02-13

2014-02-13 999

999