Процессор взаимодействует с оперативной памятью не напрямую, а через специальный контроллер, подключенный к системной шине процессора приблизительно так же, как и остальные контроллеры периферийных устройств. Причем механизм обращения к портам ввода/вывода и к ячейкам оперативной памяти с точки зрения процессора практически идентичен. Процессор сначала выставляет на адресную шину требуемый адрес, а в следующем такте уточняет тип запроса: происходит ли обращение к памяти, портам ввода/вывода или подтверждение прерывания. В некотором смысле оперативную память можно рассматривать как совокупность регистров ввода/вывода, каждый из которых хранит некоторое значение.

Обработка запросов процессора ложится на набор системной логики (так же называемый чипсетом), среди прочего включающий в себя и контроллер памяти. Контроллер памяти полностью "прозрачен" для программиста, однако знание его архитектурных особенностей существенно облегчает оптимизацию обмена с памятью.

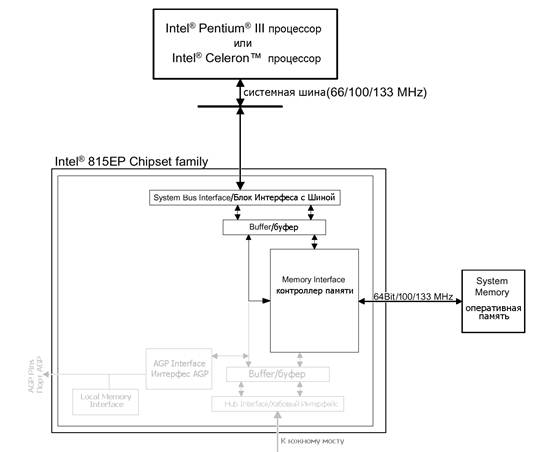

Рассмотрим механизм взаимодействия памяти и процессора на примере чипсета Intel 815EP (рис. 2.9). Когда процессору требуется получить содержимое ячейки оперативной памяти, он, дождавшись освобождения шины, через механизм арбитража захватывает шину в свое владение (что занимает один такт) и в следующем такте передает адрес искомой ячейки. Еще один такт уходит на уточнение типа запроса, назначение уникального идентификатора транзакции, сообщение длины запроса и маскировку байтов шины. Подробнее об этом можно прочитать в спецификациях на шины Р6 и EV6, здесь же достаточно отметить, что эта фаза запроса осуществляется за три такта системной шины.

Устройство северного моста чипсета Intel 815EP, содержащего (среди прочего) контроллер памяти

Независимо от размера читаемой ячейки (байт, слово, двойное слово) длина запроса всегда равна размеру линейки Ь2-кэша (подробнее об устройстве кэша мы поговорим в одноименной главе), что составляет 32 байт для процессоров K6/P-II/P-III, 64 байт — для AMD Athlon и 128 байт — для Р-4. Такое решение значительно увеличивает производительность памяти при последовательном чтении ячеек и практически не уменьшает ее при чтении ячеек вразброс, что и неудивительно, т. к. латентность чипсета в несколько раз превышает реальное время передачи данных, и им можно пренебречь.

Контроллер шины (BIU — Bus Interface Init), "вживленный" в северный мост чипсета, получив запрос от процессора, в зависимости от ситуации либо передает его соответствующему агенту (в нашем случае — контроллеру памяти), либо ставит запрос в очередь, если агент в этот момент чем-то занят. Потребность в очереди объясняется тем, что процессор может посылать очередной запрос, не дожидаясь завершения обработки предыдущего, а раз так, то запросы приходится где-то хранить.

Но, так или иначе, наш запрос оказывается у контроллера памяти (МСТ — Memory Controller). В течение одного такта он декодирует полученный адрес в физический номер строки/столбца ячейки и передает его модулю памяти по сценарию, описанному в разд. "Устройство и принципы функционирования оперативной памяти" этой главы.

В зависимости от архитектуры контроллера памяти он работает с памятью либо только на частоте системной шины (синхронный контроллер), либо поддерживает память любой другой частоты (асинхронный контроллер). Синхронные контролеры ограничивают пользователей ПК в выборе модулей памяти, но, с другой стороны, асинхронные контроллеры менее производительны. Почему? Во-первых, в силу несоответствия частот, читаемые данные не могут быть непосредственно переданы на контроллер шины, и их приходится сначала складывать в промежуточный буфер, откуда шинный контроллер сможет их извлекать с нужной ему скоростью. (Аналогичная ситуация наблюдается и с записью.) Во-вторых, если частота системной шины и частота памяти не соотносятся как целые числа, то перед началом обмена приходится дожидаться завершения текущего тактового импульса. Таких задержек (в просторечии пенальти) возникает две:

- при передаче микросхеме памяти адреса требуемой ячейки

- при передаче считанных данных шинному контроллеру.

Все это значительно увеличивает латентность подсистемы памяти — т. е. промежутка времени с момента посылки запроса до получения данных. Таким образом, асинхронный контроллер, работающий с памятью SDRAM PC-133 на системной шине в 100 МГц, проигрывает своему синхронному собрату, работающему на той же шине с памятью SDRAM PC-100.

Контроллер шины, получив от контроллера памяти уведомление о том, что запрошенные данные готовы, дожидается освобождения шины, и передает их процессору в пакетном режиме. В зависимости от типа шины за один такт может передаваться от одной до четырех порций данных. Так, в процессорах Кб, Р-И и Р-Ш осуществляется одна передача за такт, в процессоре Athlon — две, а в процессоре Р-4 — четыре.

С этого момента данные поступают в кэш и становятся доступными процессору.

Контроллер системной шины, отвечающий за обработку запросов и перемещение данных между процессором и чипсетом, состоит из следующих функциональных компонентов: трансфера данных (Processor Source Synch Clock Transceiver), планировщика запросов (Command Queue — CQ), контроллера очередей запросов (Control System Queue — CSQ) и агента транзакций (transaction combiner agent — XCA). Остальные компоненты контроллера шины, присутствующие на рис. 2.11, необходимы для поддержки зондовой отладки, которая к обсуждаемой теме не относится, а потому здесь не рассматривается.

Трансфер данных — в каком-то высшем смысле представляет собой "голый" контроллер шины, понимающий шинный протокол и берущий на себя все заботы по общению с процессором. Полученные от процессора запросы передаются планировщику запросов, откуда они отправляются соответствующим агентам по мере их освобождения.

Ответы агентов сохраняются в трех раздельных очередях: очереди чтения (SysDC Read Queue — SRQ), очереди записи памяти (Memory Write Queue — MWQ) и очереди записи шины PCI(PCI/A-PCI Write Queue — AWQ). Обратите внимание: в данном случае речь идет о записи/чтении в процессор, а не наоборот! Таким образом, очередь записи памяти хранит данные, передаваемые из памяти в процессор, но не записываемые процессором в память!

2014-01-24

2014-01-24 4391

4391