Элементы памяти. Триггерные схемы.

Триггер – это устройство, которое может находиться в одном из двух устойчивых состояний (0 или 1) в течении определенного промежутка времени, т.о. триггер – это простейшее устройство, для хранения одного бита информации.

Триггеры могут использоваться в схемах как отдельно, так и в составе устройств (регистров, счетчиков).

По законам функционирования триггеры делятся на 4 основных типа:

1. RS;

2. D;

3. JK;

4. T.

По способу синхронизации триггеры делятся на:

- асинхронные;

- синхронные.

Синхронные триггеры:

- одноступенчатые;

- двуступенчатые.

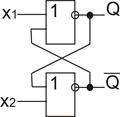

Рассмотрим схему на двух элементах «2ИЛИ-НЕ» с обратной связью и выполним анализ ее функционирования с помощью таблицы истинности.

Наличие обратной связи обеспечивает время запоминания предыдущего состояния. Схема симметрична, но стандартна. Выход обозначается  и

и  . Эта схема является триггерной, а тип уточняется по таблице истинности.

. Эта схема является триггерной, а тип уточняется по таблице истинности.

Таблица истинности (прямая таблица переходов триггера)

| x1 (R) | x2 (S) | Qt | Qt+1 | Сост |

| Save | ||||

| Set | ||||

| Reset | ||||

| * | Запр. комбинация | |||

| * |

Определим активный уровень сигнала для базового элемента («ИЛИ-НЕ»):

1 – активный,

0 – пассивный.

1) x1 = x2 = 0:  .

.

Вывод: При двух пассивных сигналах на внешних выходах триггер хранит

предыдущее состояние.

2) x1 = 0, x2 = 1:  , через 10 нс.

, через 10 нс.

Еще через 10 нс (t1+t2=20нс) на выходе первого элемента установится стабильное значение «1».

3) x1 = 1, x2 = 0.

Т.к. схема симметрична, то значения выходов поменяются.

4) x1=x2=1:

,

,

.

.

Таким образом,  , что противоречит закону функционирования устройства и является не стабильным состоянием.

, что противоречит закону функционирования устройства и является не стабильным состоянием.

Активность двух внешних входов является запрещенной комбинацией и обозначается *.

Активность входа x2 приводит к комбинации Set, поэтому x2 называют S, по аналогичной причине вход x1 называют R.

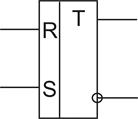

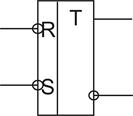

Условное графическое обозначение асинхронного RS триггера:

Вывод: Схема на двух элементах «2ИЛИ-НЕ» соответствует асинхронному RS триггеру с прямым управлением (т.к. активный уровень – «1»).

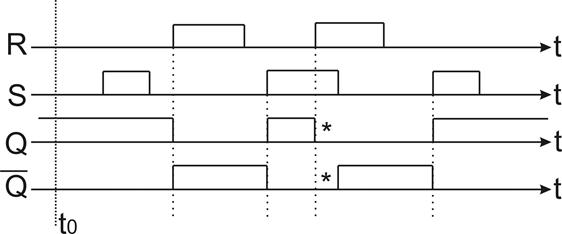

Пример временной диаграммы:

Чтобы заполнить временную диаграмму необходимо задать импульсы на входы сигналов R и S, выбрать момент начала отсчета t0, задать состояние входа Q до начала отсчета.

Решение заключается в том, чтобы заполнить ось выхода Q, соответственно таблице истинности триггера, т.е. показать влияние комбинации входных сигналов на состояние выхода, т.е. на формирование сигнала на выходе.

Обратная таблица переходов:

| Qt | Qt+1 | R | S |

| * | |||

| * |

8.2 Асинхронный  триггер (базовая ячейка памяти)

триггер (базовая ячейка памяти)

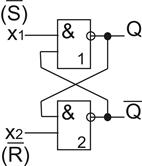

Исследуем схему с обратной связью, построенную на двух элементах «2И-НЕ». Анализ выполним используя таблицу истинности.

Таблица истинности (прямая таблица переходов триггера):

x1 ( ) )

| x2 ( ) )

| Qt | Qt+1 | Сост |

| * | Запр. комбинация | |||

| * | ||||

| Set | ||||

| Reset | ||||

| Save | ||||

Для функции «И» активный уровень – «0», а пассивный – «1».

1) x1=x2=0:  – запрещенная комбинация.

– запрещенная комбинация.

2) x1=0, x2=1.  ->

->  , Set.

, Set.

3) x1=1, x2=0. ->

->  , Reset.

, Reset.

4) x1=x2=1:  .

.

Условное графическое обозначение асинхронного  триггера:

триггера:

Инверсии на входах обозначаю то, что триггеры управляются нулем.

Вывод: Данная схема соответствует одноступенчатому асинхронному RS триггеру с инверсным управлением ( - триггер). Эта схема является базовой, для построения схем других типов.

- триггер). Эта схема является базовой, для построения схем других типов.

2014-02-24

2014-02-24 3236

3236