Для реализации неполного дешифратора:

1. Можно взять стандартную микросхему полного DC и использовать необходимое количество выходов. Но такое решение является избыточным.

2. Можно синтезировать неполный DC, как комбинационнцю схему с минимизацией аппаратных затрат.

Пример. Синтезировать DC 3à5

Таблица истинности:

| X1 | X2 | X3 | Y0 | Y1 | Y2 | Y3 | Y4 |

| * | * | * | * | * | |||

| * | * | * | * | * | |||

| * | * | * | * | * |

В таблице имеется неопределенность (*), которая дает возможность минимизации выходных функций y0-y4.

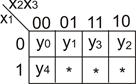

В общем случае для каждой функции необходима своя карта Карно, но в данном случае каждая функция активна только на единственно соответствующем ей наборе сигналов x1, x2, x3, поэтому составим одну общую карту Карно, в которой вместо единиц укажем соответствующие функции yi.

Склеивать разные функции нельзя. Можно использовать только *.

Из карты Карно получили следующие формулы:

Логическая схема данного дешифратора имеет вид:

Сравним цену по кванту в случае использования полного DC и комбинационной схемы неполного DC.

Для полного: СКВ = 3*2 + 3*8 = 30 входов

Для КС неполного DC:

СКВ = 3*2 + 3 + 3*2 = 15 входов

Вывод: Очевидно, цена по кванту минимизированной схемы неполного DC 3à5 дает эффект 50%.

2014-02-24

2014-02-24 1687

1687