Пример 9.1

Определить логическую функцию, реализуемую представленной схемой на рис.9.2.

Решение будем вести последовательно, находя значение функции в точках схемы, отмеченных цифрами. Для упрощений используем соотношения из приложения Б.

Таким образом, у = x1 Å х2; b = x1 ^ х2). Результаты обработки могут быть представлены в виде таблицы:

Поскольку перечисленные преобразования являются правилами двоичного суммирования, рассмотренная комбинация логических элементов получила название полусумматора. На ее вход подаются два сигнала: x1 и х2; выходной сигнал у дает результат сложения в том же двоичном разряде, в котором стоят складываемые числа; в случае суммирования 1 + 1 происходит перенос в старший разряд - для него имеется еще один выход b. В арифметико-логическом устройстве компьютера полусумматор обрабатывает лишь младшие разряды регистров. Для всех остальных разрядов помимо двух складываемых значений необходимо учитывать бит переноса, образовавшийся в результате сложения предыдущих разрядов. Следовательно, комбинационная схема, обеспечивающая выполнение данной операции, должна иметь три входа (x1, х2 и bi-1) и формировать два выходных значения (у и bn) - эта схема называется двоичным сумматором. Логические функции такой схемы для каждого из разрядов i (i = 2 ... п, считая, что младшим является разряд 1):

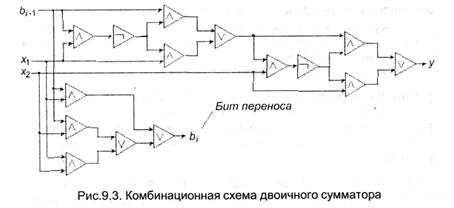

Схема, реализующая такие логические функции - она называется последовательным двоичным сумматором - содержит 15 логических элементов (9 И, 4 ИЛИ и 2 НЕ). Схема двоичного сумматора представлена на рис. 9.3. Такой сумматор обеспечивает выполнение операций в одном из разрядов процессора. Следовательно, 32-разрядный процессор будет содержать 31 схему сумматора и1 полусумматора (для младшего разряда), которые соединены друг с другом и вместе образуют сумматор.

Подобным образом, вообще говоря, можно построить комбинационную схему для любого конечного множества задач, решение которых (т.е. выходные сигналы) однозначно определяются их условием (т.е. входными сигналами). В частности, если ограничиться некоторой фиксированной точностью представления числа, то можно построить комбинационную схему, которая вычисляет значение любой функции у = f(x1,...xn) (безусловно, в двоичных кодах), например, sin(x) и др. Однако на практике получается, что при разрядности 32 и выше даже схема умножителя, вычисляющего произведение х1∙х2, становится столь сложной, что оказывается проще реализовать умножение иным путем, который можно назвать алгоритмическим и который позволяет представить умножение в виде последовательности сложений и сдвигов, о чем шла речь ранее. Точно также и иные вычисления сводятся к цепочкам элементарных операций: сложение, сдвиг, инверсия и пр. |

|

Организация структур данных в ОЗУ Формы представления информации Таким образом - формулировки и наиболее важные утверждения. Вернуться в оглавление: Теоретические основы информатики |