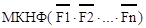

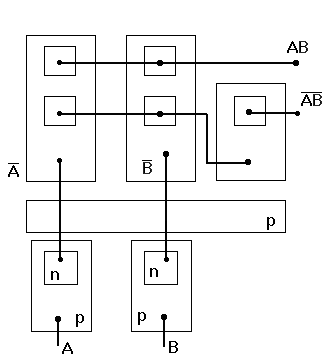

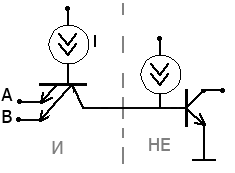

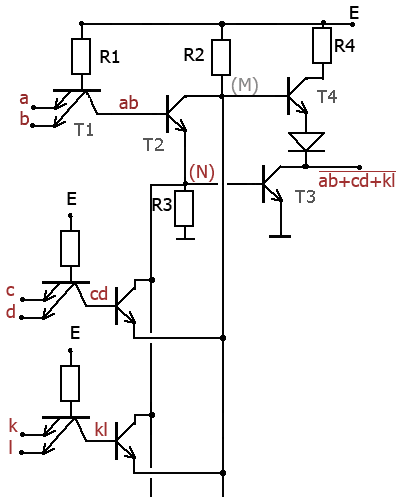

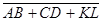

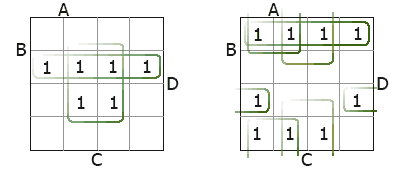

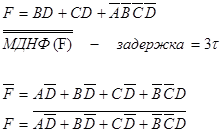

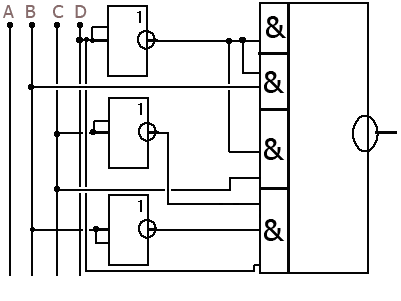

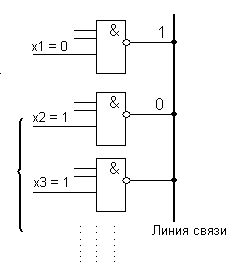

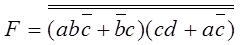

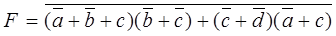

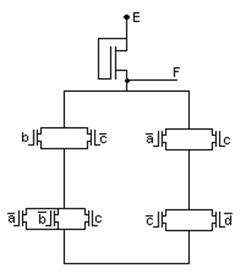

Для того, чтобы спроектировать сколь угодно сложное устройство в базисе И2Л, необходимо взять МКНФ функции. Затем взять двойное почленное отрицание и раскрыть внутреннее.

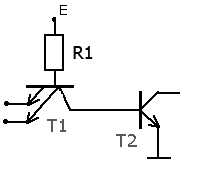

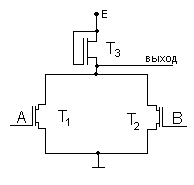

Монтажное И реализуется только тогда, когда аргументы снимаются с выходов инжекционных инверторов.

Лекция 9

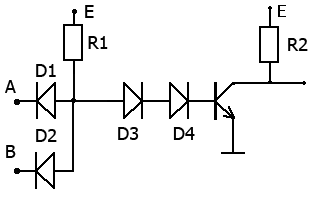

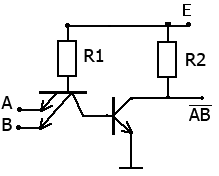

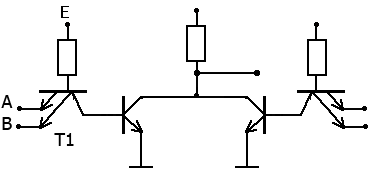

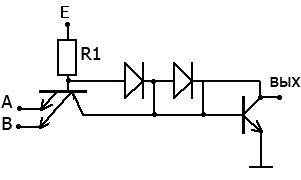

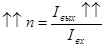

Реализация функции И-НЕ в биполярной схемотехнике.

ДТЛ – диодно-транзисторная логика.

Докажем, что эта схема реализует эту функцию.

Логика – Л+.

| А | В | D1 | D2 | D3 | D4 | T | вых |

|

| отк. | отк. | зак. | Е | |||||

| отк. | зак. | зак. | Е | |||||

| зак. | отк. | зак. | Е | |||||

| зак. | зак. | отк. | отк. | нас. | Uкэн |

Вывод: Схема ДТЛ может содержать один или больше диодов сопряжения.

Достоинства и недостатки ДТЛ.

Недостатки:

- Очень большая мощность

- Большая задержка

- Много транзисторов, поэтому большая площадь

Достоинство

- Большая помехоустойчивость

Если п/п области различных компонентов имеют одинаковый потенциал, то их можно объединить в одну область.

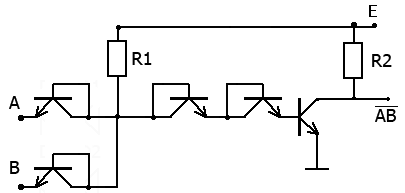

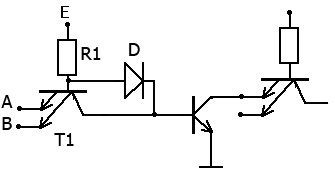

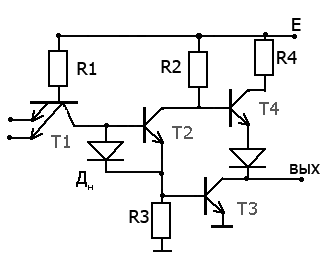

Результатом оптимизации является многоэмиттерный транзистор ТТЛ.

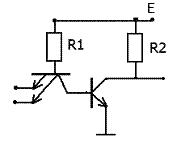

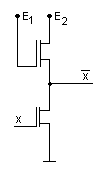

Схема ТТЛ с простым инвертором.

Логика – Л+.

| A | B | МЭТ | Т | выход | |

| б-э1 отрыт б-э2 отрыт | E1R1 закрыт | n=0 »E | |||

| б-э1 отрыт б-э2 зарыт | закрыт | »E | |||

| б-э1 зарыт б-э2 отрыт | закрыт | »E | |||

| б-э1 зарыт б-э2 зарыт | насыщен | Uкэн (0.1 ¸ 0.2 В) |

Достоинства и недостатки ТТЛ с простым инвертором.

В сравнении с ДТЛ:

Достоинства:

- Маленькая площадь

- Маленькая мощность

- Маленькая задержка

Недостатки:

- Низкая помехоустойчивость

Объективно:

Недостатки:

- Низкая помехоустойчивость

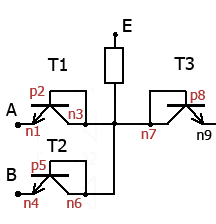

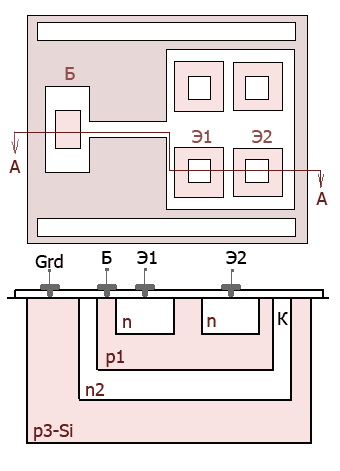

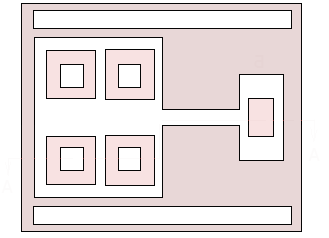

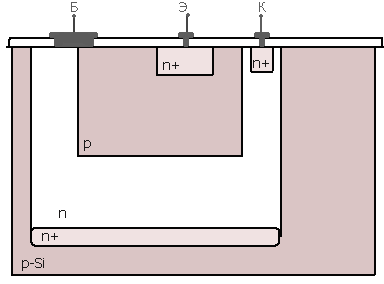

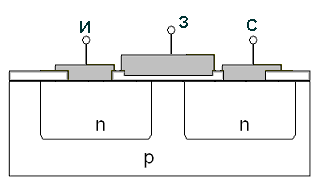

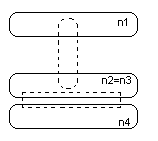

Топология.

Существует паразитный транзистор p1 – n2 – p3

p1 – база

n2 – коллектор

p3 – Gound

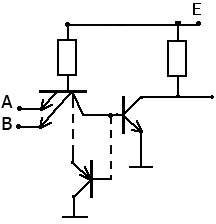

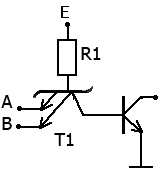

Модификации ТТЛ с простым инвертором.

1.

ТТЛ с открытым коллектором. Данная схема используется для реализации дополнительных логических функций.

2.

3.

4.

5.

Эта схема не требует нагрузки.

U1 = E – 2UD – IR

t = 1.1 + IR + 2UD

Лекция 10

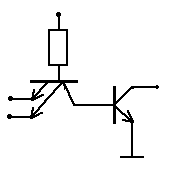

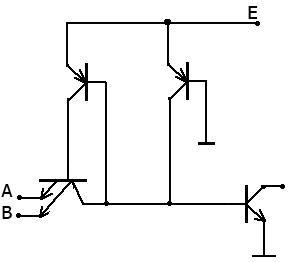

Синтез комплиментарной схемы ТТЛ с простым инвертором.

Fсв1 = (1, 2, 3, 4, 5, 6)

Fсв2 = (1, 2, 3, 4, 5, 6)

Класс ТТЛ с простым инвертором.

Недостатки:

- n = 3 ¸ 4

- есть сопротивление

- есть паразитный транзистор

- низкое быстродействие

Достоинства:

- с ДТЛ кроме Uп

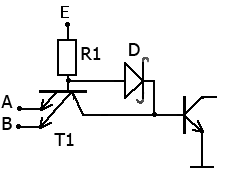

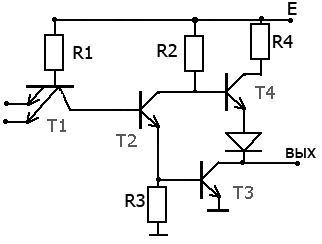

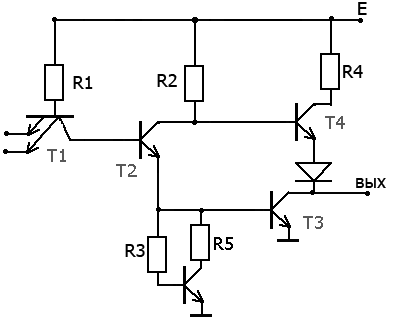

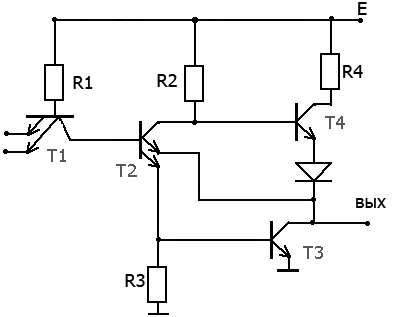

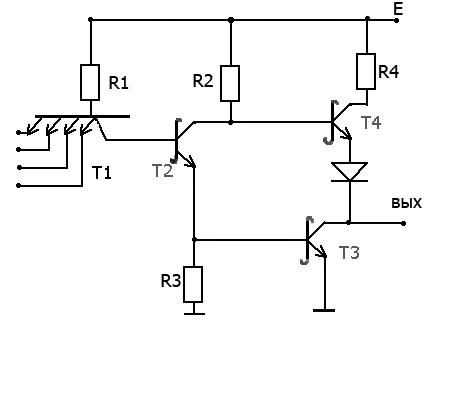

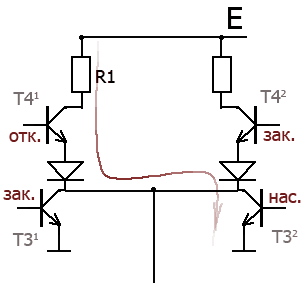

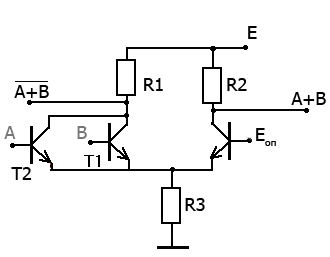

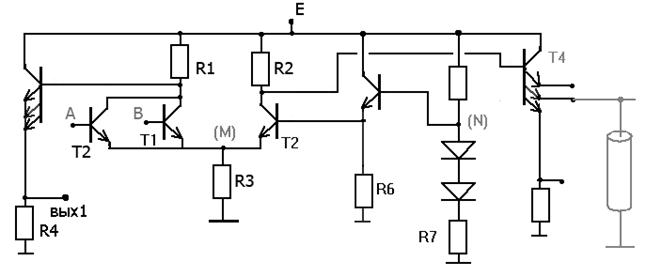

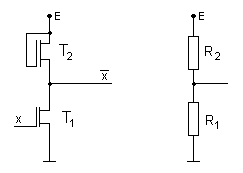

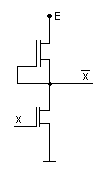

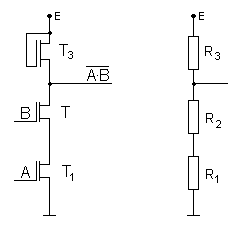

Класс ТТЛ со сложным инвертором.

Логика – Л+.

Т1 выполняет функцию U.

Т2 и Т3 обеспечивают запас помехоустойчивости.

Диод D используется для запирания транзистора Т4, когда на выходе “0”.

Т3, Т4 – пара антагонистов. Они увеличивают быстродействие, когда Т3 закрыт и на выходе “1”. В этом случае выходное сопротивление определяется сопротивлением Т4.

| А | В | Т1 | Т2 | Т3 | Т4 | выход | |

| б-э1 – отк б-э2 – отк | закрыт | закрыт | открыт | U = E-IR2-Uбэ4-UD > U0+Uл | |||

| б-э1 – отк б-э2 – зак | закрыт | закрыт | открыт | U = E-IR2-Uбэ4-UD | |||

| б-э1 – зак б-э2 – отк | закрыт | закрыт | открыт | U = E-IR2-Uбэ4-UD | |||

| б-э1 – зак б-э2 – зак | насыщен | насыщен | закрыт | U = Uкэн = 0.1 ¸0.2 В |

Достоинства:

- малое время задержки - t = 10 нс.

- высокая нагрузочная способность n > 30 ¸ 40

- большой запас помехоустойчивости

Недостатки:

· много компонентов

· есть сопротивление

· большая мощность

· большая площадь

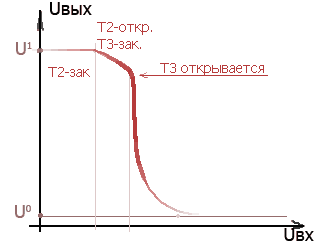

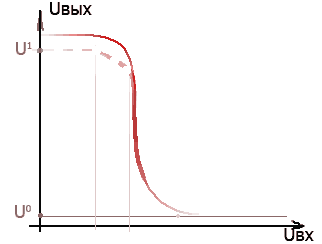

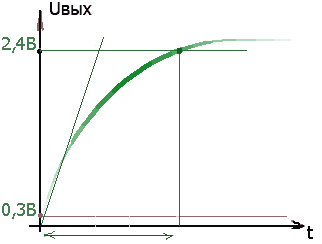

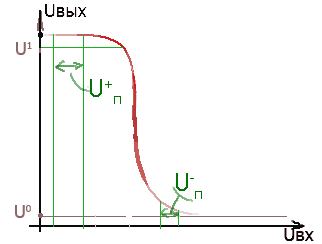

Передаточная характеристика.

Как видно из графика – передаточная характеристика неидеальная. Неидеальная передаточная характеристика может привести к нелогичной работе всего устройства.

Лекция 11

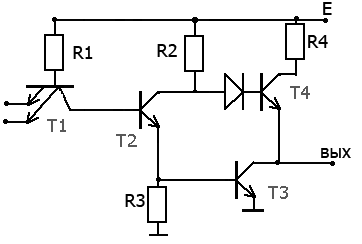

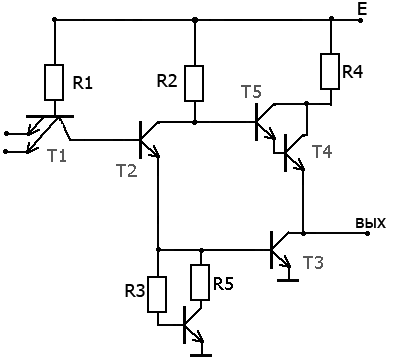

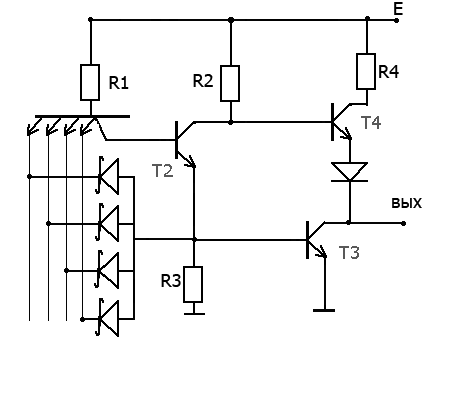

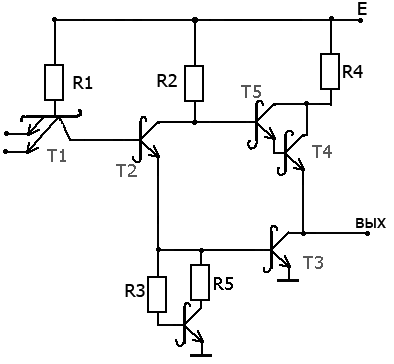

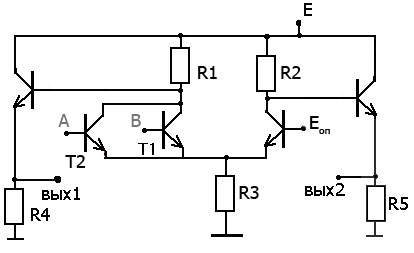

Модификации схемы ТТЛ со сложным инвертором (варианты оптимизации).

1. Схема отличается от стандартной тем, что диод из эмиттерной цепи Т4 перенесен в базовую.

Для исправления передаточной характеристики используется схема оптимизации 2.

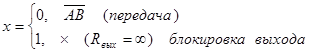

2. В этой схеме вместо сопротивления R3 используется ключ R3-R5-T5. Транзистор Т3 открывается только тогда, когда будет открыт не только Т2, но и Т5. А Т2 и Т5 открываются одновременно. Фактически, Т2-Т5 – это как бы единый транзистор.

3. Оптимизация нагрузочной способности.

- нагрузочная способность

- нагрузочная способность

Быстродействие здесь становится немного хуже, т.к. емкость увеличивается.

Транзисторы Т4-Т5 составляют пару Дарлингтона.

Улучшение быстродействия схемы ТТЛ со сложным инвертором.

Алгоритмы улучшения:

1. быстро уменьшать заряды Q2, Q3

или

2. не накапливать эти заряды.

4. Использование медленного диода.

При подаче запирающего напряжения диод еще открыт.

Const = Q = ¯t * Ip

Ip – ток рассасывания

Медленный диод формирует низкоомный путь для рассасывания Q3.

5.

Данный вариант способствует уменьшению Q3.

¯Q3 ® ¯ tp

tp – время рассасывания.

6. Использование диодов Шоттки.

Диоды Шоттки формируют низкоомный путь для отвода Q3 из базы насыщенного транзистора Т3.

7. Схема, в которой Q2=Q3=0 в режиме насыщения.

Qi=0

tТТЛШ = 3 нс

tТТЛ = 10 нс

Лекция 12

Стандартная ТТЛ Шоттки.

Достоинства:

- min t

- max n

- max Uп

Недостатки:

- S

- kR ® P * t

- Uкэн = 0.4 ¸ 0.5 В

ТТЛ с расширителем И-ИЛИ-НЕ.

- на выходе.

- на выходе.

Здесь может быть шесть расширителей (определяется режимом работы и задержки).

Расширитель:

Пример:

F = (0, 3, 5, 7, 11, 13, 15)

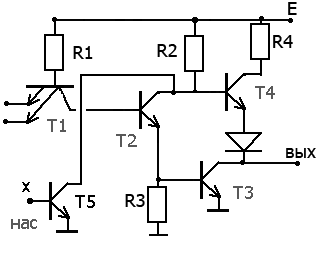

ТТЛ с тремя состояниями.

В БИС у простых ТТЛ существуют проблемы.

Для устранения этой проблемы используют схему ТТЛ с тремя состояниями.

| x | A | B | T1 | T2 | T3 | T4 | T5 | выход |

| закрыт | ||||||||

| закрыт | ||||||||

| закрыт | ||||||||

| закрыт | ||||||||

| закрыт | закрыт | насыщен | ´ | |||||

| закрыт | закрыт | насыщен | ´ | |||||

| закрыт | закрыт | насыщен | ´ | |||||

| закрыт | закрыт | насыщен | ´ |

Лекция 13

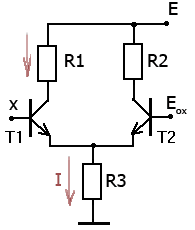

Эмиттерно Связанная Логика - ЭСЛ.

МЭСЛ (маломощная ЭСЛ)

Логика – Л+

|

| |||||

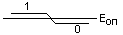

| x < Eоп | x | Выход 1 | Выход 2 | Uбэ1 < Uбэ2 | ||

В данном случае – относительно положительная логика.

То, что немного больше Еоп – это логическая единица, меньше – ноль.

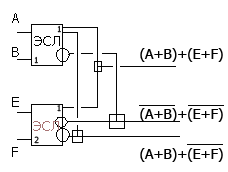

Зависимую функцию ИЛИ можно реализовать, включив вместо транзистора Т1 параллельно транзисторы Т11 и Т12.

Достоинства:

- Функционально полный базис

- Маленький логический перепад

Недостатки:

- Маленькая помехоустойчивость

- Есть сопротивления

- Rвых = [кОм] Þ большое время задержки

С = t ~ (Rвых * Cп)

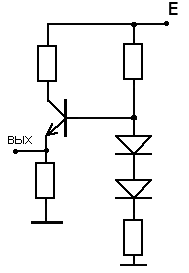

Чтобы уменьшить Rвых и уменьшить задержку, надо к выходу подключить эмиттерный повторитель.

// Пометим эту схему (*****)

Эмиттерные повторители на выходе позволяют реализовать дополнительную функцию ИЛИ.

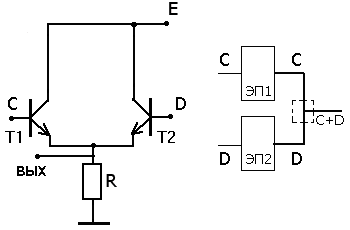

| С | D | T1 | T2 | выход | |

| закрыт | закрыт | ||||

| закрыт | открыт | IR | |||

| открыт | закрыт | IR | |||

| открыт | открыт | IR |

Пример:

Вывод: использование эмиттерных повторителей в ЭСЛ дает два преимущества.

- увеличение быстродействия за счет уменьшения входного сопротивления

- реализацию дополнительной логической функции монтажное ИЛИ (параллельное соединение эмиттерных повторителей)

Существует и недостаток у этих схем – это два источника напряжения. Поэтому наша задача – уменьшить количество источников питания.

Использование схемы опорного напряжения.

Вставляем этот кусочек в схему (*****) и получаем:

Т.к. в точке N имеется встречное включение одинакового количества p-n переходов, то любое изменение температуры будет компенсировано.

Схема ЭСЛ с отрицательным питанием.

Недостаток схемы с положительным питанием заключается в том, что напряжение логического нуля и единицы определяются в зависимости от Е.

U1 = (Е ± DЕ) – IR1R1 – Uбэ

U0 = (Е ± DЕ) – IR2R2 – Uбэ

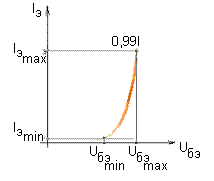

IR1 = 0.01I

IR2 = 0.99I

У источника питания существует разброс, как логический, так и температурный.

Е ± DЕ

Замечательный метод.

Если из всех узловых потенциалов схемы вычесть некоторую константу, то работа схемы не изменится.

Для схемы с отрицательным питанием U0 и U1 будет определяться так:

U1 = 0 – IR1R1 - Uбэ

U0 = 0 – IR2R2 - Uбэ

0 = Ground

Лекция 14

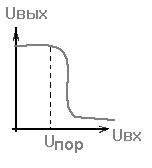

Схемотехника МОП вентилей. МОП инвертор.

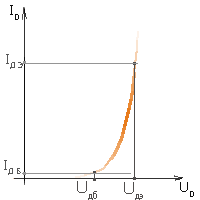

Чем больше Uпор, тем выше запас помехоустойчивости схем.

Uпор формирует питание элемента.

1.

2.

3.

Рассмотрим схему 1.

| x | T1 | T2 | выход | Прим. | |

| Нет канала, закрыт по U | Есть канал, открыт по U | ~E | |||

| Есть канал, открыт по U | Есть канал, открыт по U | G1 >> G2 |

Схема 2 – это инвертор, у которого каналы нагрузочного транзистора управляются каналом. Этот инвертор с улучшенным быстродействием, с наименьшей задержкой.

Схема 3 – схема с улучшенной мощностью.

Достоинства:

- высокий запас помехоустойчивости

- маленькая потребляемая мощность

- стоимость много меньше, чем у биполяров

Недостатки:

- большая задержка (плохое быстродействие)

- неустойчив к радиации

- разные топологии транзисторов (логического и нагрузочного)

МОП вентиль И-НЕ.

| А | В | Т1 | Т2 | Т3 | Выход | Прим. | |

| закрыт | закрыт | открыт | Е | ||||

| закрыт | открыт по U закрыт по I | открыт | Е | ||||

| закрыт по току | закрыт | открыт | Е | ||||

| открыт | ® ground | G3 << (G1+G2) |

Недостаток схемы: Напряжение питания зависит от количества аргументов.

МОП вентиль ИЛИ-НЕ.

Т1-Т2 – логическая часть

Т3 – нагрузочная часть

| А | В | Т1 | Т2 | Т3 | Выход | Прим. | |

| закрыт | закрыт | открыт | Е | ||||

| открыт | открыт | ~0 B | Если R2 <<R3 | ||||

| открыт | открыт | ~0 B | R1 << R3 | ||||

| открыт | открыт | открыт | ~0 B | R3 >> (R2 || R1) |

С увеличением количества вентилей в данной схеме ухудшается задержка.

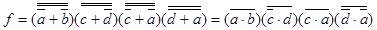

Основные принципы синтеза МОП схем.

Общая инверсия реализуется с помощью нагрузочного транзистора.

Зависимое (подинверсное) умножение реализуется с помощью последовательного включения транзисторов или схем.

Зависимое (подинверсное) сложение реализуется с помощью параллельного включения транзисторов или схем.

Пример:

Лекция 15

Схемотехника КМОП схем.

2014-02-24

2014-02-24 941

941