Составить схему счетчика-делителя на N, где N = <№ варианта> + 5.

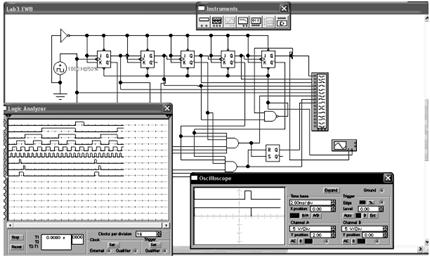

6.1. Составить принципиальную схему счетчика-делителя на N на базе D-триггеров или JK-триггеров для своего варианта работы.6.2. Смоделировать электрическую функциональную схему счетчика в среде Electronics Workbench. 6.3. Включить схему и, подавая на вход схемы тактовые импульсы, убедиться в правильности работы счетчика.6.4. Получить временные диаграммы входных и выходных сигналов для смоделированного счетчика с помощью логического анализатора Logic Analizer и двухлучевого осциллографа.Общие сведения и методические указания

по выполнению заданий

Цифровые устройства, в которых выходное состояние зависит не только от того, какие сигналы присутствуют на его входах в данный момент времени, но и в предшествующие моменты, называют последовательностными, или многотактными автоматами. Типичным таким устройством является триггер.

Триггер – это последовательностная схема с двумя устойчивыми состояниями Каждому из этих состояний ставится в соответствие логическое значение, которое хранит триггер (логическая 1 или логический 0 в зависимости от уровня выходного сигнала).

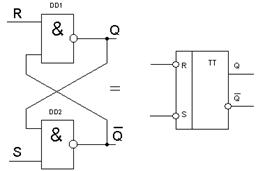

Несмотря на большое разнообразие триггеров, практически все они строятся на базе простейших базовых RS-триггеров (рис. 6.1).

Один из входов триггера называется установочным входом и обозначается буквой S (от слова Set), а другой – входом сброса и обозначается буквой R (от слова Reset). Триггер имеет два симметричных выхода: прямой и инверсный.

| S | R | Q |

| Сохраняется прежнее значение | ||

| Запрещено! |

Рис. 6.1. RS-триггер и его таблица состояний

По способу записи информации различают триггеры синхронные и асинхронные (тактируемые). В асинхронных триггерах запись информации осуществляется непосредственно с поступлением информации на вход, в синхронных – только при подаче синхронизирующего импульса. Условие четкой работы такого триггера – это временное совпадение синхроимпульсов и подаваемой на входы R и S информации. В противном случае возможна потеря информации.

По способу записи информации различают триггеры синхронные и асинхронные (тактируемые). В асинхронных триггерах запись информации осуществляется непосредственно с поступлением информации на вход, в синхронных – только при подаче синхронизирующего импульса. Условие четкой работы такого триггера – это временное совпадение синхроимпульсов и подаваемой на входы R и S информации. В противном случае возможна потеря информации.

Для устранения такого недостатка приме-няются D-триггеры (Delay – задержка). При работе такого триггера происходит задержка выходного сигнала на один рабочий такт, что исключает потерю информации.

D-триггер имеет один информационный вход D, вход синхронизации С и два выхода прямой Q и инверсный  (рис. 6.2).

(рис. 6.2).

Т-триггеры (Toggle – кувыркаться) применяются для построения счетчиков импульсов, они, как правило, имеют счетный вход и два выхода прямой Q и инверсный

Т-триггеры (Toggle – кувыркаться) применяются для построения счетчиков импульсов, они, как правило, имеют счетный вход и два выхода прямой Q и инверсный  . (рис. 6.3).

. (рис. 6.3).

При поступлении каждого сигнала на счетный вход триггера его выходы меняют свое состояние на противоположное.

В интегральном исполнении приме-няется обычно синхронный, универсальный JK-триггер, который имеет два информа-ционных входа J и K, вход синхрониза-ции С и два выхода прямой Y и инверсный

В интегральном исполнении приме-няется обычно синхронный, универсальный JK-триггер, который имеет два информа-ционных входа J и K, вход синхрониза-ции С и два выхода прямой Y и инверсный  (рис. 6.4).

(рис. 6.4).

Применяя входную логику, на основе JK-триггера можно построить любой тип из ранее рассмотренных триггеров (RS-, D- и

T-триггеры).

Каждый из триггеров дополнительно имеет, как правило, R и/или S установочные входы.

Следует отметить, что самостоятельно RS-триггеры в устройствах цифровой техники практически не используются из-за их низкой помехоустойчивости. Например, короткие импульсы помехи, попадающие на R и S входы, могут изменить состояние триггера.

Для повышения помехоустойчивости и устранения так называемых «состязаний» используют синхронный RS-триггер, который изменяет свое состояние только в те моменты времени, когда на специальный синхровход триггера С поступает разрешающий тактирующий импульс.

Рассмотренные выше RS-триггеры нельзя использовать в цифровых устройствах с обратными связями, так как изменения на входах и выходах происходят практически одновременно, что может привести к неопределенностям.

Для устойчивой работы RS-триггера, в том числе и в схемах с обратными связями, необходимо, чтобы сигналы на выходах изменялись только тогда, когда его входы заперты, т.е. синхросигнал уже прекратился. Это требование выполняется в двухступенчатых триггерах (MS-триггерах).

MS-триггер состоит из двух секций, соединенных каскадно. Для ведущего триггера используется обычная синхронизация, в то время как для ведомого триггера импульс синхронизации инвертируется. Изменение состояния выхода ведущего триггера будет происходить в момент появления положительного импульса синхронизации, и эти изменения будут переданы на входы ведомого триггера. Однако никакие изменения на выходе ведомого триггера не будут происходить до тех пор, пока не появится отрицательный фронт исходного синхроимпульса. Такая синхронизация называется динамической. Динамические триггеры могут переключаться как передним, так и задним фронтом тактирующих импульсов.

Одним из самых широко используемых триггеров является

Одним из самых широко используемых триггеров является

D-триггер, который называют информационным триггером, а также триггером задержки. Он бывает только синхронным. Может управляться как уровнем тактирующего импульса, так и его фронтом. По синхроимпульсу D-триггер принимает то состояние, которое имеет входная линия D. Обычно в одном корпусе ИМС содержатся два D-триггера, управляемых фронтом. D-триггеры в интегральном исполнении имеют также дополнительные асинхронные входы управления S и R (входы «предустановки» и «очистки»).

Среди триггеров особое место занимают JK-триггеры, имеющие более широкие функциональные возможности. Упрощенная таблица состояний JK-триггера содержит четыре строки.

Выпускаемые промышленностью ИМС JK-триггеры могут иметь несколько входов (до трех) J и такое же количество входов K, объединенных схемами конъюнкций. Т-триггер – это счетный триггер. Он имеет один вход, куда подают тактирующие (счетные) импульсы. Каждый синхроимпульс меняет состояние Т-триггера на обратное (аналогично состоянию JK-триггера при комбинации входных переменных J = 1 и K = 1). Частота следования импульсов на выходе счетного триггера в два раза меньше частоты входных синхроимпульсов, что позволяет их использовать в качестве делителей частоты. Для реализации делителя частоты на четыре потребуются два триггера, соединенных последовательно и т.д. Т-триггеры строятся только на базе двухступенчатых (RS, D, JK) триггеров.

Счетчики импульсов

На базе счетных триггеров можно построить цифровое устройство, получившее название электронного счетчика, которое позволяют вести подсчет электрических импульсов, поступивших на их вход. Счетчики импульсов – неотъемлемые узлы микропроцессоров, микрокалькуляторов, электронных часов, таймеров частотометров и многих других устройств цифровой техники. Основу их составляют триггеры со счетным входом.

Простейшим одноразрядным счетчиком импульсов является JK-триггер или D-триггер, работающий в счетном режиме. Он считает входные импульсы по модулю 2: каждый импульс переключает триггер в противоположное состояние. Результат счета формируется

в заданном коде, который может храниться в памяти счетчика или быть считанным другим устройством цифровой техники – дешифратором.

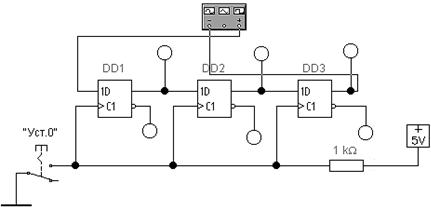

На рис. 6.5 приведена схема трехразрядного двоичного счетчика импульсов.

Рис. 6.5. Трехразрядный двоичный счетчик

Если в начальный момент все триггеры счетчика находились в нулевом состоянии (можно установить кнопочным выключателем «Уст.0», подавая на R входы триггеров напряжение низкого уровня), по спаду первого импульса триггер DD1 переключится в единичное состояние – на его прямом выходе появится высокий уровень напряжения. Второй импульс переключит триггер DD1 в нулевое состояние, а триггер DD2 – в единичное. По спаду третьего импульса триггеры DD1 и DD2 окажутся в единичном состоянии, а триггер DD3 все еще будет в нулевом. Четвертый импульс переключит первых два триггера в нулевое состояние, а третий – в единичное. Восьмой импульс переключит все триггеры в нулевое состояние, начнется следующий цикл работы счетчика импульсов. Число различных состояний N-разрядного счетчика  .

.

Счетчики-делители считают входные импульсы до некоторого задаваемого коэффициентом счета состояния, а затем формируют сигнал сброса триггеров в нулевое состояние, вновь начинают счет входных импульсов до задаваемого коэффициента счета и т.д. Коэффициент деления счетчика, состоящего из N-триггеров типа Т, составляет  ; здесь N – число двоичных разрядов счетчика. Коэффициент деления счетчика может быть либо постоянным, либо переключаемым. Основой любой из счетной схем служит линейка из нескольких триггеров. Разные варианты счетных схем (синхронные и асинхронные; однонаправленные, только с увеличением счета, и двунаправленные, счет в которых может увеличиваться или уменьшаться) различаются схемой управления этими триггерами. Между триггерами добавляются логические связи, назначение которых – запретить прохождение в цикле счета лишним импульсам. К примеру, четырехтриггерный счетчик может делить исходную частоту на 16, так как

; здесь N – число двоичных разрядов счетчика. Коэффициент деления счетчика может быть либо постоянным, либо переключаемым. Основой любой из счетной схем служит линейка из нескольких триггеров. Разные варианты счетных схем (синхронные и асинхронные; однонаправленные, только с увеличением счета, и двунаправленные, счет в которых может увеличиваться или уменьшаться) различаются схемой управления этими триггерами. Между триггерами добавляются логические связи, назначение которых – запретить прохождение в цикле счета лишним импульсам. К примеру, четырехтриггерный счетчик может делить исходную частоту на 16, так как  =16. Получим минимальный выходной

=16. Получим минимальный выходной

код 0000, а максимальный 1111. Чтобы построить счетчик-делитель на 10, трех триггеров не достаточно (10>  ), поэтому десятичный счетчик содержит в своей основе четыре триггера, но имеет обратные связи, останавливающие счет при коде 9 = 1001. В синхронном счетчике все триггеры получают тактовый импульс одновременно, поскольку тактовые входы их соединяются параллельно. Поэтому триггеры переключаются практически одновременно. В счетчике пульсаций каждый триггер вносит в процесс счета определенную задержку, поэтому младшие разряды результирующего кода появляются на выходах триггеров неодновременно, т.е. несинхронно с соответствующим тактовым импульсом. Например, для четырехразрядного счетчика пульсаций выходной параллельный код 1111 появится на выходах триггеров уже после того, как поступит шестнадцатый тактовый импульс, кроме того, эти четыре единицы сформируются неодновременно.

), поэтому десятичный счетчик содержит в своей основе четыре триггера, но имеет обратные связи, останавливающие счет при коде 9 = 1001. В синхронном счетчике все триггеры получают тактовый импульс одновременно, поскольку тактовые входы их соединяются параллельно. Поэтому триггеры переключаются практически одновременно. В счетчике пульсаций каждый триггер вносит в процесс счета определенную задержку, поэтому младшие разряды результирующего кода появляются на выходах триггеров неодновременно, т.е. несинхронно с соответствующим тактовым импульсом. Например, для четырехразрядного счетчика пульсаций выходной параллельный код 1111 появится на выходах триггеров уже после того, как поступит шестнадцатый тактовый импульс, кроме того, эти четыре единицы сформируются неодновременно.

Синхронная схема значительно сложнее асинхронной. На ее выходах данные от каждого разряда появляются одновременно и строго синхронно с последним входным импульсом.

Сброс данных счетчика, чтобы на всех выходах установился нулевой код, у одних схем асинхронный R, у других синхронный SR, происходит одновременно с приходом тактового импульса. Имеются счетчики с переменным коэффициентом деления. Устанавливаемый коэффициент деления зависит от кода, набранного на входах управления.

Далее приведены примеры различных счетчиков. На базе примеров разработайте свою схему и выполните задание.

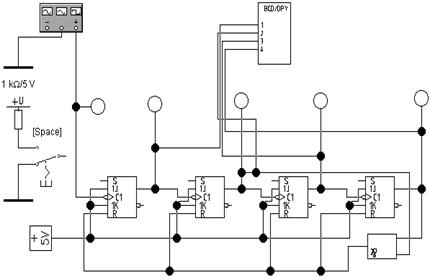

Рис. 6.6. Пример двоично-десятичного счетчика

Рис. 6.7. Пример счетчика на JK-триггерах со схемой выборки

и совпадения для изменения коэффициента пересчета

Контрольные вопросы и задания

6.1. Приведите схему подключения логического анализатора Logic Analizer к счетчику.

6.2. Приведите схему выборки и совпадения для двоично-десятичного счетчика.

6.3. Почему RS-триггер имеет низкую помехозащищенность?

6.1. Какой максимальный коэффициент пересчета для N-разрядного счетчика?

6.2. Почему JK-триггер называют универсальным?

6.3. Можно ли на трехразрядном счетчике получить коэффициент деления 9?

6.4. Поясните принцип работы делителя частоты.

Литература

6.1. Методические указания для выполнения лабораторных работ по дисциплине «Информационно-измерительная техника и электроника». – М.: МИЭЭ, 2006. – 24 с.

6.2. https://ru.wikipedia.org/wiki/Триггер – материал по триггерам из Википедии.

6.3. https://www.tstu.ru/education/elib/pdf/2005/chernva.pdf – счетчики импульсов.

6.4. https://naf-st.ru/articles/digit/count/ – цифровые счетчики.

6.5. https://venec.ulstu.ru/lib/disk/2007/137.pdf – Вычислительная техника и информационные технологии: сборник лабораторных работ. – Ульяновск: УлГТУ, 2007. – Ч. 1: Цифровая схемотехника. – 30 c.

2015-01-30

2015-01-30 2361

2361